Nowe kody redukują szumy, które uniemożliwiają skalowanie komputerów kwantowych

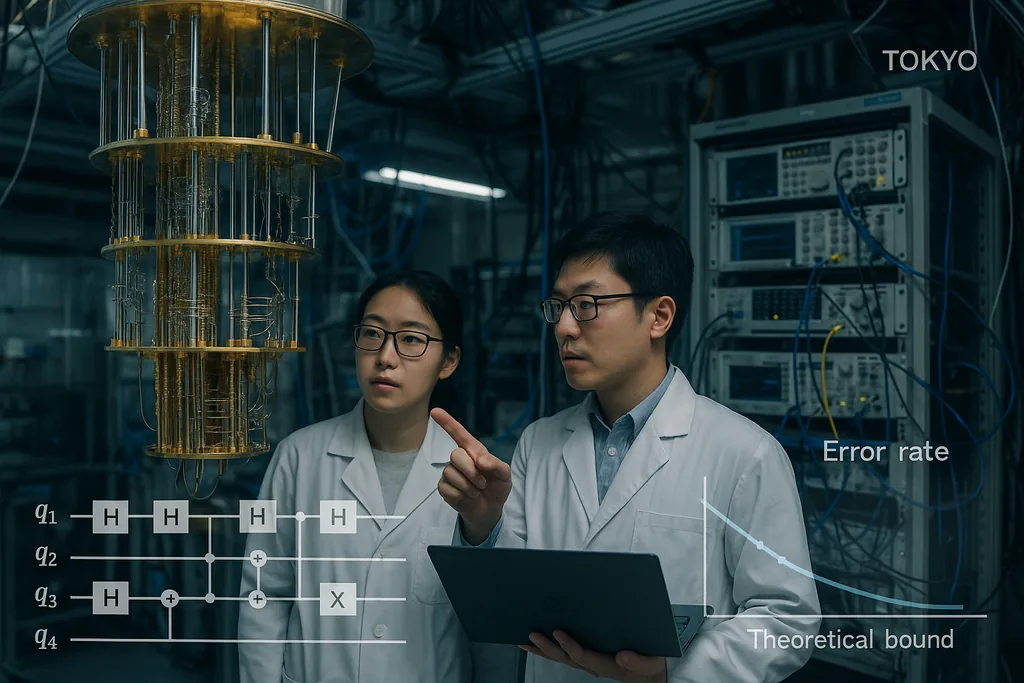

30 września 2025 roku zespół z Tokio opublikował artykuł przedstawiający kwantowe kody korekcji błędów, które zbliżają się wyjątkowo blisko do długo utrzymującej się teoretycznej granicy dla niezawodnej komunikacji i obliczeń kwantowych — tak zwanej granicy haszowania (hashing bound) — pozostając jednocześnie wydajnie dekodowalnymi. Wynik, wyróżniony obecnie w publikacjach instytucjonalnych, nie jest prostym, magicznym rozwiązaniem; to staranne przeprojektowanie konstrukcji kodów LDPC (o niskiej gęstości kontroli parzystości) oraz ich dekoderów, które wspólnie obniżają wskaźniki błędów ramek do praktycznych poziomów i utrzymują niski narzut obliczeniowy. Te dwie cechy — wydajność bliska przepustowości kanału oraz koszt dekodowania skalujący się liniowo wraz z maszyną — są właśnie tymi właściwościami, których potrzeba, aby przenieść procesory kwantowe z fazy laboratoryjnych ciekawostek do maszyn zdolnych do rozwiązywania rzeczywistych problemów w chemii, kryptografii i nauce o klimacie.

Kod bliski przepustowości dla szumnego kanału kwantowego

Granica haszowania to sufit informacyjno-teoretyczny: wyznacza ona najwyższą prędkość, z jaką informacja kwantowa może być niezawodnie przesyłana przez szumny kanał przy użyciu optymalnego kodowania i dekodowania. Historycznie, kwantowe kody o udowodnionej wydajności znajdowały się daleko od tego limitu lub wymagały niepraktycznie obciążających dekoderów. Demonstrując kody, które zarówno zbliżają się do tej granicy, jak i mogą być dekodowane przy użyciu zasobów klasycznych o umiarkowanej skali, Komoto i Kasai przedstawiają przekonujący argument, że skalowanie sprzętu — przedsięwzięcie polegające na połączeniu milionów fizycznych kubitów w celu uzyskania wielu kubitów logicznych — jest realistycznym celem inżynieryjnym, a nie tylko teoretyczną mrzonką.

Dekodery: niedoceniane wąskie gardło staje się rozwiązanym problemem

Kody korekcji błędów to tylko połowa sukcesu; drugą połowę stanowią szybkie i dokładne dekodery. W ciągu ostatniego roku kilka przełomów algorytmicznych pozwoliło zniwelować wąskie gardło dekodowania. W czerwcu 2025 roku naukowcy opisali PLANAR, algorytm dokładnego dekodowania dla określonych topologii kodów, który zmienia pozornie nierozwiązywalny problem dekodowania największej wiarygodności w wydajnie obliczalną funkcję podziału szkła spinowego na grafach planarnych. Po zastosowaniu do danych eksperymentalnych, PLANAR znacząco zredukował wskaźniki błędów logicznych i wykazał, że część tego, co wyglądało na ograniczenia sprzętowe, w rzeczywistości wynikało z suboptymalnego dekodera. To spostrzeżenie ma kluczowe znaczenie, ponieważ oznacza, że lepsze dekodery mogą wycisnąć większą wydajność z istniejących urządzeń bez żadnych zmian w sprzęcie kwantowym.

Od strony inżynieryjnej zespoły przemysłowe przenoszą te koncepcje dekodowania do klasycznego sprzętu działającego w czasie rzeczywistym. IBM poinformował niedawno, że kluczowy algorytm korekcji błędów może działać na konwencjonalnych układach FPGA firmy AMD wystarczająco szybko, by zapewnić sprzężenie zwrotne w czasie rzeczywistym w systemach nadprzewodzących, demonstrując działanie znacznie wykraczające poza prędkość wymaganą dla wielu architektur. Uruchamianie dekoderów na dostępnych klasycznych chipach to milowy krok: przekształca korekcję błędów z kosztownego procesu programowego offline w praktyczną usługę o niskich opóźnieniach, którą można osadzić w stosach sterujących dużych maszyn. W połączeniu z kodami bliskimi przepustowości, szybkie dekodery sprzętowe zamykają lukę między teorią a systemami gotowymi do wdrożenia.

Co ta zbieżność oznacza dla rzeczywistych zastosowań

Zastosowania kwantowe, które obiecują przełomową wartość — symulacje molekularne do opracowywania leków, optymalizacja logistyki czy nowe prymitywy kryptograficzne — zazwyczaj wymagają milionów logicznych kubitów lub ekstremalnie niskich wskaźników błędów logicznych utrzymywanych podczas długich obliczeń. Do tej pory te szacunki zasobów przekładały się na astronomiczne liczby fizycznych kubitów, ponieważ korekcja błędów charakteryzowała się zarówno słabymi progami, jak i kosztownymi dekoderami. Połączenie konstrukcji kodowania Komoto i Kasai, ulepszonych dekoderów takich jak PLANAR oraz dążenia do uruchamiania dekodowania na standardowym klasycznym sprzęcie, w zasadzie znacząco obniża ten narzut. To zmienia układ sił: generacja sprzętu kwantowego, która wcześniej była oceniana jako niepraktyczna, może być teraz w zasięgu ręki, jeśli zespoły inżynieryjne zdołają dostarczyć macierze kubitów o umiarkowanej skali z oczekiwaną wiernością fizyczną.

Istnieją już ścieżki zorientowane na zastosowania, które bazują na tych pracach. Na przykład naukowcy badający kwantowe uczenie maszynowe wykazali, że częściowa lub przybliżona korekcja błędów może sprawić, iż krótkoterminowe modele kwantowe będą znacznie bardziej praktyczne niż wcześniej, zmniejszając wymagania sprzętowe niezbędne do uzyskania przewagi. Takie synergie między teorią kodowania, przybliżoną odpornością na błędy a projektowaniem algorytmów mogą przyspieszyć praktyczne zastosowania na maszynach pośrednich, jeszcze przed nadejściem pełnej tolerancji na błędy.

Bariery, które pozostają

Mimo postępów, pozostaje kilka trudnych problemów inżynieryjnych i fizycznych. Kody i dekodery opisane w pracy Komoto–Kasai zostały zademonstrowane w symulacjach i badaniach numerycznych; przeniesienie ich do krzemu, obwodów nadprzewodzących, pułapkowanych jonów czy układów fotonicznych wymaga zaprojektowania potoków dekodujących z ekstremalnymi gwarancjami czasu rzeczywistego, przesłania milionów sygnałów przez stosy kriogeniczne oraz tłumienia rzadkich, ale niszczycielskich efektów, takich jak skorelowane błędy wywołane promieniowaniem kosmicznym. Implementacja niebinarnej arytmetyki ciał skończonych w sprzęcie, integracja ekstrakcji syndromów bez dodawania szumu oraz walidacja wydajności w realistycznych modelach szumu urządzeń to nietrywialne zadania, które zdecydują o tym, czy obietnica numeryczna stanie się rzeczywistością operacyjną.

W grze są również konkurencyjne strategie sprzętowe. Niektóre grupy poprawiają wewnętrzną odporność sprzętu na błędy — na przykład podejścia fotoniczne i oparte na kubitach typu „cat-qubit” deklarują inne kompromisy między naturalnym ukierunkowaniem szumu a liczbą zasobów — a testowanie porównawcze (benchmarking) tych architektur będzie niezbędne w miarę udostępniania skalowalnych dekoderów. Nie każda architektura będzie w stanie równie dobrze wykorzystać każdy kod lub dekoder, dlatego społeczność nadal potrzebuje walidacji międzyplatformowej.

Od teorii do inżynierii: następne kroki

Dalsza droga wygląda jak skoordynowany, trójtorowy program. Po pierwsze, projektanci kodów będą dopracowywać konstrukcje, aby radziły sobie z bardziej realistycznymi modelami szumu i błędami skorelowanymi oraz by jeszcze bardziej obniżyć poziom błędów szczątkowych (error floors). Po drugie, zespoły od dekoderów będą nadal redukować opóźnienia i koszty energii oraz portować algorytmy na układy FPGA, ASIC i, tam gdzie to konieczne, do logiki kriogenicznej. Po trzecie, grupy sprzętowe będą testować kody i dekodery na rzeczywistych urządzeniach, raportując nie tylko wskaźniki błędów logicznych, ale także ukryte koszty infrastruktury: obliczenia klasyczne, okablowanie, chłodzenie i konserwację. Jeśli te trzy tory się zbiegną, społeczność będzie w stanie zamienić abstrakcyjną obietnicę przewagi kwantowej w konkretne mapy drogowe dla maszyn wykonujących użyteczną pracę.

Krótko mówiąc, niedawne prace nad kodami LDPC bliskimi granicy haszowania nie są odizolowanym triumfem, lecz najnowszym, przekonującym sygnałem, że połączenie inteligentniejszych kodów, lepszych dekoderów i praktycznej integracji z klasycznym sprzętem może zamknąć lukę między teorią a zastosowaniem. Harmonogram dla szeroko użytecznych obliczeń kwantowych pozostaje niepewny, ale te postępy realnie wzmacniają argumenty inżynieryjne za budową następnej generacji maszyn, które spróbują wykonać realną pracę dla przemysłu i nauki.

Źródła

- npj Quantum Information (Komoto & Kasai: „Quantum error correction near the coding theoretical bound”).

- Physical Review Letters (Cao et al.: „Exact Decoding of Quantum Error‑Correcting Codes”).

- Materiały prasowe Institute of Science Tokyo podsumowujące prace Komoto & Kasai.

- Komunikaty badawcze i raporty IBM dotyczące implementacji dekoderów kwantowych na FPGA.

Comments

No comments yet. Be the first!