Nuovi codici riducono il rumore che impedisce la scalabilità dei computer quantistici

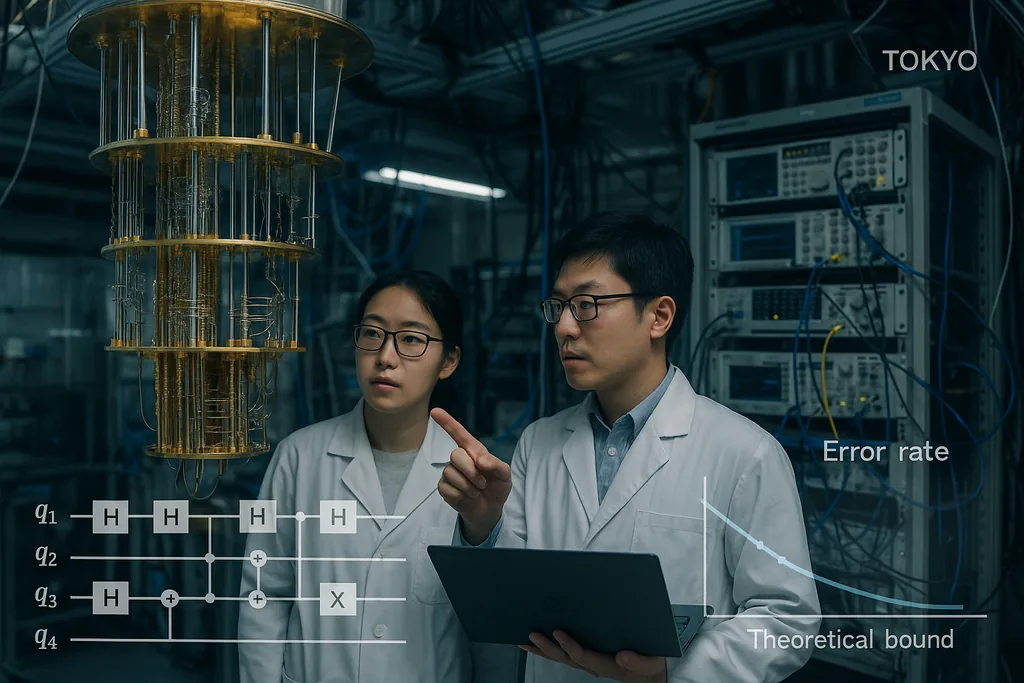

Il 30 settembre 2025, un team di Tokyo ha pubblicato un articolo che presenta codici di correzione degli errori quantistici che si avvicinano insolitamente al limite teorico storico per una comunicazione e un calcolo quantistico affidabili — il cosiddetto limite di hashing (hashing bound) — pur rimanendo efficientemente decodificabili. Il risultato, ora evidenziato in vari report istituzionali, non è una soluzione magica immediata; si tratta di una meticolosa riprogettazione delle strutture low-density parity-check (LDPC) e dei relativi decodificatori che, insieme, riducono i tassi di errore di frame a livelli pratici e mantengono basso l'overhead computazionale. Queste due caratteristiche — prestazioni vicine alla capacità e costi di decodifica che scalano linearmente con la macchina — sono proprio le proprietà necessarie per far passare i processori quantistici da curiosità di laboratorio a macchine in grado di affrontare problemi reali in chimica, crittografia e scienza del clima.

Un codice vicino alla capacità per il canale quantistico rumoroso

Il limite di hashing è un tetto teorico dell'informazione: segna la velocità massima alla quale l'informazione quantistica può essere trasmessa in modo affidabile attraverso un canale rumoroso utilizzando codifica e decodifica ottimali. Storicamente, i codici quantistici dimostratamente efficienti sono stati lontani da tale limite o hanno richiesto decodificatori impraticabili per la loro complessità. Dimostrando codici che si avvicinano al limite e che possono essere decodificati con risorse classiche che scalano moderatamente, Komoto e Kasai sostengono in modo convincente che la scalabilità dell'hardware — il progetto di cablare milioni di qubit fisici per generare molti qubit logici — sia un obiettivo ingegneristico realistico piuttosto che un sogno teorico irraggiungibile.

Decodificatori: il collo di bottiglia trascurato sta diventando un problema risolto

I codici di correzione degli errori sono solo metà dell'opera; decodificatori veloci e precisi sono l'altra metà. Nell'ultimo anno, diversi progressi algoritmici hanno intaccato il collo di bottiglia della decodifica. Nel giugno 2025, i ricercatori hanno descritto PLANAR, un algoritmo di decodifica esatta per determinate topologie di codice che trasforma un problema di decodifica a massima verosimiglianza, apparentemente intrattabile, in un calcolo della funzione di partizione di vetri di spin (spin-glass) su grafi planari efficientemente risolvibile. Applicato ai dati sperimentali, PLANAR ha ridotto significativamente i tassi di errore logico e ha dimostrato che parte di quelli che sembravano limiti hardware erano in realtà dovuti a un decodificatore subottimale. Questa intuizione è fondamentale perché significa che decodificatori migliori possono estrarre maggiori prestazioni dai dispositivi esistenti senza alcuna modifica all'hardware quantistico.

Sul fronte ingegneristico, i team industriali stanno portando queste idee di decodifica nell'hardware classico in tempo reale. IBM ha recentemente riferito che un algoritmo chiave di correzione degli errori può essere eseguito su FPGA AMD convenzionali abbastanza velocemente da consentire un feedback in tempo reale nei sistemi a superconduzione, dimostrando un funzionamento ben oltre la velocità necessaria per molte architetture. L'esecuzione dei decodificatori su chip classici accessibili è un passo cruciale: trasforma la correzione degli errori da un processo software offline e costoso in un servizio pratico a bassa latenza che può essere integrato negli stack di controllo per macchine di grandi dimensioni. Insieme ai codici vicini alla capacità, i decodificatori hardware veloci chiudono il cerchio tra teoria e sistemi implementabili.

Cosa significa questa convergenza per le applicazioni reali

Le applicazioni quantistiche che promettono un valore trasformativo — simulazione molecolare per la scoperta di farmaci, ottimizzazione per la logistica o nuove primitive crittografiche — richiedono tipicamente milioni di qubit logici o tassi di errore logico estremamente bassi sostenuti su calcoli lunghi. Finora, queste stime delle risorse si traducevano in conteggi astronomici di qubit fisici perché la correzione degli errori presentava soglie scarse e decodificatori costosi. La combinazione delle strutture di codifica di Komoto e Kasai, dei decodificatori migliorati come PLANAR e della spinta a eseguire la decodifica su hardware classico standard riduce sostanzialmente questo overhead in linea di principio. Ciò sposta l'equilibrio: una generazione di hardware quantistico precedentemente giudicata impraticabile potrebbe ora essere a portata di mano, se i team di ingegneri riusciranno a fornire array di qubit su scala moderata con le fedeltà fisiche previste.

Esistono già filoni orientati alle applicazioni che si basano su questo lavoro. Ad esempio, i ricercatori che esplorano il machine learning quantistico hanno dimostrato che una correzione degli errori parziale o approssimativa può rendere i modelli quantistici a breve termine molto più pratici di prima, riducendo le richieste hardware necessarie per osservare un vantaggio. Tali sinergie tra teoria dei codici, tolleranza ai guasti approssimativa e progettazione di algoritmi potrebbero accelerare gli usi pratici su macchine intermedie anche prima dell'arrivo di una completa tolleranza ai guasti.

Le barriere che rimangono

Nonostante i progressi, rimangono diversi difficili problemi di ingegneria e fisica. I codici e i decodificatori nell'articolo di Komoto–Kasai sono dimostrati in simulazioni e studi numerici; trasferirli su silicio, circuiti a superconduzione, ioni intrappolati o configurazioni fotoniche richiede la progettazione di pipeline di decodifica con garanzie estreme di tempo reale, l'instradamento di milioni di segnali attraverso stack criogenici e la soppressione di effetti rari ma devastanti come gli errori correlati indotti dai raggi cosmici. L'implementazione di aritmetica dei campi finiti non binari nell'hardware, l'integrazione dell'estrazione della sindrome senza aggiungere rumore e la convalida delle prestazioni in modelli di rumore dei dispositivi realistici sono compiti non banali che determineranno se la promessa numerica diventerà una realtà operativa.

Vi sono anche strategie hardware concorrenti in gioco. Alcuni gruppi stanno migliorando la resilienza intrinseca agli errori dell'hardware — ad esempio, gli approcci fotonici e i cat-qubit dichiarano diversi compromessi tra bias del rumore naturale e conteggio delle risorse — e il benchmarking tra queste architetture sarà essenziale man mano che diventeranno disponibili decodificatori scalabili. Non tutte le architetture saranno in grado di sfruttare ogni codice o decodificatore allo stesso modo, quindi la comunità necessita ancora di una validazione cross-platform.

Dalla teoria all'ingegneria: i prossimi passi

Il percorso da seguire appare come un programma coordinato su tre binari. In primo luogo, i progettisti di codici affineranno le strutture per gestire modelli di rumore più realistici ed errori correlati, e per abbassare ulteriormente le soglie di errore. In secondo luogo, i team dei decodificatori continueranno a ridurre la latenza e i costi energetici e a portare gli algoritmi su FPGA, ASIC e logica criogenica ove necessario. In terzo luogo, i gruppi hardware testeranno codici e decodificatori su dispositivi reali, riportando non solo i tassi di errore logico ma anche i costi infrastrutturali nascosti: calcolo classico, cablaggio, raffreddamento e manutenzione. Se questi tre binari convergeranno, la comunità sarà in grado di trasformare l'astratta promessa del vantaggio quantistico in roadmap concrete per macchine che svolgano un lavoro utile.

In breve, il recente lavoro sui codici LDPC vicini al limite di hashing non è un trionfo isolato, ma l'ultimo, convincente segno che una combinazione di codici più intelligenti, decodificatori migliori e una pratica integrazione dell'hardware classico può colmare il divario tra teoria e applicazione. La tempistica per un calcolo quantistico ampiamente utile rimane incerta, ma questi progressi migliorano materialmente il caso ingegneristico per la costruzione della prossima generazione di macchine che cercheranno di svolgere un lavoro reale per l'industria e la scienza.

Fonti

- npj Quantum Information (Komoto & Kasai: "Quantum error correction near the coding theoretical bound").

- Physical Review Letters (Cao et al.: "Exact Decoding of Quantum Error‑Correcting Codes").

- Materiali stampa dell'Institute of Science Tokyo che riassumono il lavoro di Komoto & Kasai.

- Comunicazioni di ricerca IBM e report sulle implementazioni FPGA di decodificatori quantistici.

Comments

No comments yet. Be the first!