양자 컴퓨터의 확장을 가로막는 노이즈를 줄여주는 새로운 부호 기술

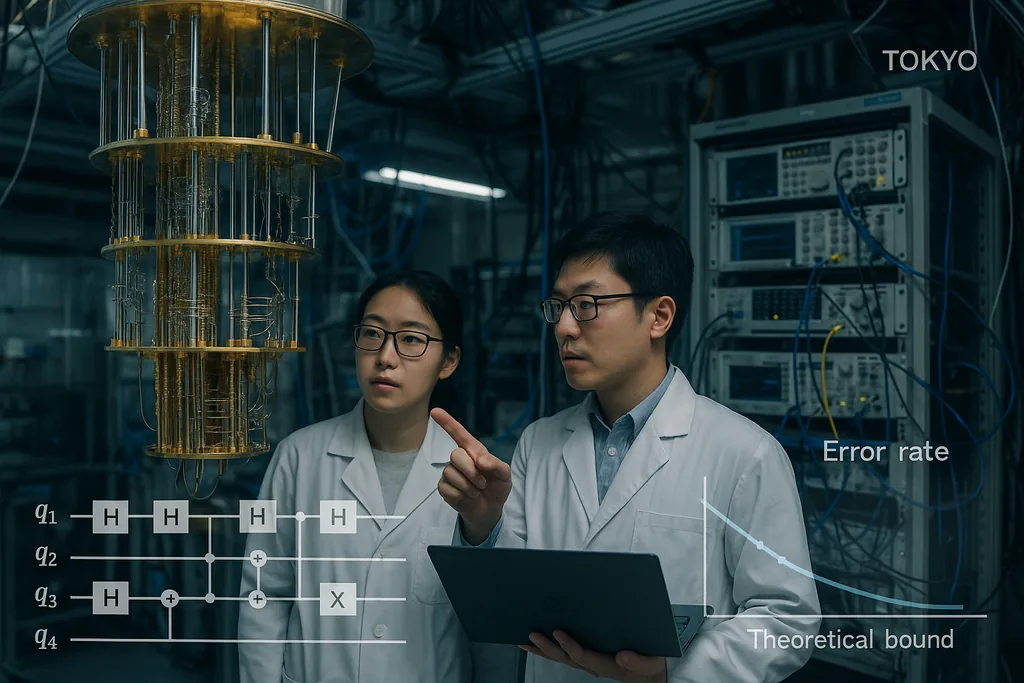

2025년 9월 30일, 도쿄의 한 연구팀은 효율적인 복호화가 가능하면서도 신뢰할 수 있는 양자 통신 및 컴퓨팅의 오랜 이론적 한계인 소위 '해싱 바운드(hashing bound)'에 이례적으로 근접한 양자 오류 정정 부호를 발표했다. 기관 보고서에서 강조된 이 결과는 단 한 줄의 마법 같은 해결책이 아니라, 프레임 오류율을 실용적인 수준으로 낮추고 컴퓨팅 오버헤드를 낮게 유지하는 저밀도 패리티 검사(LDPC) 구조와 복호화기를 정밀하게 재설계한 결과다. 용량에 근접한 성능과 장치 규모에 따라 선형적으로 확장되는 복호화 비용이라는 이 두 가지 특징은 양자 프로세서를 실험실의 신기한 물건에서 화학, 암호학, 기후 과학의 실제 문제를 해결할 수 있는 기계로 진화시키는 데 필요한 핵심 속성이다.

노이즈가 있는 양자 채널을 위한 용량 근접 부호

해싱 바운드는 정보 이론상의 한계치다. 이는 최적의 부호화 및 복호화 기술을 사용할 때 노이즈가 있는 채널을 통해 양자 정보를 안정적으로 전송할 수 있는 최고 속도를 의미한다. 역사적으로 효율성이 입증된 양자 부호들은 이 한계에서 멀리 떨어져 있거나 비실용적으로 무거운 복호화기를 필요로 했다. Komoto와 Kasai는 한계에 근접하면서도 적당한 규모의 클래식 리소스로 복호화할 수 있는 부호를 시연함으로써, 수백만 개의 물리 큐비트를 연결하여 많은 논리 큐비트를 생성하는 하드웨어 확장 프로젝트가 이론적인 몽상이 아닌 현실적인 엔지니어링 목표임을 설득력 있게 보여주었다.

복호화기: 해결 과제로 떠오른 숨겨진 병목 현상

오류 정정 부호는 이야기의 절반에 불과하며, 빠르고 정확한 복호화기가 나머지 절반을 차지한다. 지난 한 해 동안 여러 알고리즘의 발전으로 복호화 병목 현상이 조금씩 해결되어 왔다. 2025년 6월, 연구자들은 특정 부호 토폴로지를 위한 정확한 복호화 알고리즘인 PLANAR를 설명했다. 이는 다루기 힘들어 보였던 최대 가능도(maximum-likelihood) 복호화 문제를 평면 그래프에서의 효율적으로 해결 가능한 스핀 유리 분배 함수(spin-glass partition-function) 계산으로 변환한다. PLANAR를 실험 데이터에 적용했을 때 논리 오류율이 크게 감소했으며, 하드웨어의 한계처럼 보였던 부분 중 일부가 실제로는 최적이 아닌 복호화기 때문이었음을 보여주었다. 이러한 통찰은 양자 하드웨어를 변경하지 않고도 더 나은 복호화기를 통해 기존 장치에서 더 많은 성능을 끌어낼 수 있음을 의미하기에 중요하다.

엔지니어링 측면에서 산업계 팀들은 이러한 복호화 개념을 실시간 클래식 하드웨어로 옮기고 있다. IBM은 최근 주요 오류 정정 알고리즘이 기존 AMD FPGA에서 초전도 시스템의 실시간 피드백에 충분할 만큼 빠르게 실행될 수 있음을 보고했으며, 이는 많은 아키텍처에 필요한 속도를 훨씬 뛰어넘는 작동을 입증한 것이다. 접근 가능한 클래식 칩에서 복호화기를 실행하는 것은 중요한 단계다. 이는 오류 정정을 오프라인의 비용이 많이 드는 소프트웨어 프로세스에서 대형 기계의 제어 스택에 내장될 수 있는 실용적이고 저지연적인 서비스로 변모시킨다. 용량 근접 부호와 함께 빠른 하드웨어 복호화기는 이론과 배포 가능한 시스템 사이의 고리를 완성한다.

이러한 융합이 실제 응용 분야에 갖는 의미

약물 발견을 위한 분자 시뮬레이션, 물류 최적화 또는 새로운 암호화 기본 단위와 같이 변혁적인 가치를 약속하는 양자 응용 분야에는 일반적으로 수백만 개의 논리 큐비트 또는 긴 계산 과정 동안 유지되는 극도로 낮은 논리 오류율이 필요하다. 지금까지 이러한 리소스 추정치는 오류 정정의 임계치가 낮고 복호화기 비용이 많이 들었기 때문에 천문학적인 수의 물리 큐비트로 환산되었다. Komoto와 Kasai의 부호 구조, PLANAR와 같은 개선된 복호화기, 그리고 표준 클래식 하드웨어에서 복호화를 실행하려는 노력이 결합되어 원칙적으로 그러한 오버헤드를 실질적으로 낮춘다. 이는 균형을 변화시킨다. 엔지니어링 팀이 예상되는 물리적 충실도(fidelity)를 갖춘 중간 규모의 큐비트 어레이를 제공할 수 있다면, 이전에 비실용적이라고 판단되었던 세대의 양자 하드웨어가 이제 사정권 안에 들어올 수 있다.

이 연구를 바탕으로 한 응용 중심의 흐름이 이미 형성되고 있다. 예를 들어, 양자 기계 학습을 연구하는 연구자들은 부분적 또는 근사적 오류 정정이 단기 양자 모델을 이전보다 훨씬 실용적으로 만들 수 있으며, 이득을 보는 데 필요한 하드웨어 요구 사항을 줄일 수 있음을 보여주었다. 부호 이론, 근사적 결함 허용(fault-tolerance) 및 알고리즘 설계 사이의 이러한 시너지 효과는 완전한 결함 허용이 달성되기 전이라도 중간 단계의 기계에서 실용적인 사용을 가속화할 수 있다.

여전히 남아있는 장벽들

이러한 진전에도 불구하고 몇 가지 까다로운 엔지니어링 및 물리학적 문제가 남아 있다. Komoto와 Kasai의 논문에 소개된 부호와 복호화기는 시뮬레이션 및 수치 연구를 통해 입증되었다. 이를 실리콘, 초전도 회로, 이온 트랩 또는 광자 설정으로 옮기려면 극도의 실시간 보장이 포함된 복호화 파이프라인을 설계하고, 극저온 스택을 통해 수백만 개의 신호를 라우팅하며, 우주선(cosmic-ray)으로 인한 상관 오류와 같이 드물지만 치명적인 영향을 억제해야 한다. 하드웨어에서 비이진 유한체 산술을 구현하고, 노이즈를 추가하지 않고 신드롬 추출을 통합하며, 실제 장치 노이즈 모델에서 성능을 검증하는 것은 수치적 약속이 운영상의 현실이 될지 여부를 결정할 난제들이다.

경쟁 관계에 있는 하드웨어 전략들도 존재한다. 일부 그룹은 하드웨어의 고유한 오류 복원력을 개선하고 있다. 예를 들어 광자 및 캣 큐비트(cat-qubit) 접근 방식은 자연적인 노이즈 편향과 리소스 수 사이의 서로 다른 절충안을 제시하며, 확장 가능한 복호화기가 사용 가능해짐에 따라 이러한 아키텍처 간의 벤치마킹이 필수적일 것이다. 모든 아키텍처가 모든 부호나 복호화기를 동일하게 잘 활용할 수 있는 것은 아니므로, 커뮤니티에는 여전히 교차 플랫폼 검증이 필요하다.

이론에서 엔지니어링으로: 향후 단계

앞으로의 경로는 세 가지 트랙이 조화를 이루는 프로그램이 될 것으로 보인다. 첫째, 부호 설계자들은 더 실제적인 노이즈 모델과 상관 오류를 처리하고 오류 플로어(error floors)를 더 낮추기 위해 구조를 다듬을 것이다. 둘째, 복호화기 팀은 지연 시간과 에너지 비용을 계속 줄여나가고 알고리즘을 FPGA, ASIC 및 필요한 경우 극저온 로직으로 이식할 것이다. 셋째, 하드웨어 그룹은 실제 장치에서 부호와 복호화기를 벤치마킹하여 논리 오류율뿐만 아니라 클래식 컴퓨팅, 배선, 냉각 및 유지 관리와 같은 숨겨진 인프라 비용을 보고할 것이다. 이 세 트랙이 수렴된다면, 커뮤니티는 양자 이득에 대한 추상적인 약속을 유용한 작업을 수행하는 기계를 위한 구체적인 로드맵으로 바꿀 수 있을 것이다.

요약하자면, 해싱 바운드에 근접한 LDPC 부호에 대한 최근의 연구는 고립된 성과가 아니라, 더 똑똑한 부호, 더 나은 복호화기, 그리고 실용적인 클래식 하드웨어 통합의 조합이 이론과 응용 사이의 간극을 메울 수 있다는 최신의 설득력 있는 신호다. 광범위하게 유용한 quantum computing의 타임라인은 여전히 불확실하지만, 이러한 발전은 산업과 과학을 위해 실제 작업을 수행하려는 차세대 기계를 구축하기 위한 엔지니어링 근거를 실질적으로 개선한다.

Sources

- npj Quantum Information (Komoto & Kasai: "Quantum error correction near the coding theoretical bound").

- Physical Review Letters (Cao et al.: "Exact Decoding of Quantum Error‑Correcting Codes").

- Institute of Science Tokyo press materials summarising the Komoto & Kasai work.

- IBM research disclosures and reporting on FPGA implementations of quantum decoders.

Comments

No comments yet. Be the first!