Nuevos códigos reducen el ruido que impide el escalado de las computadoras cuánticas

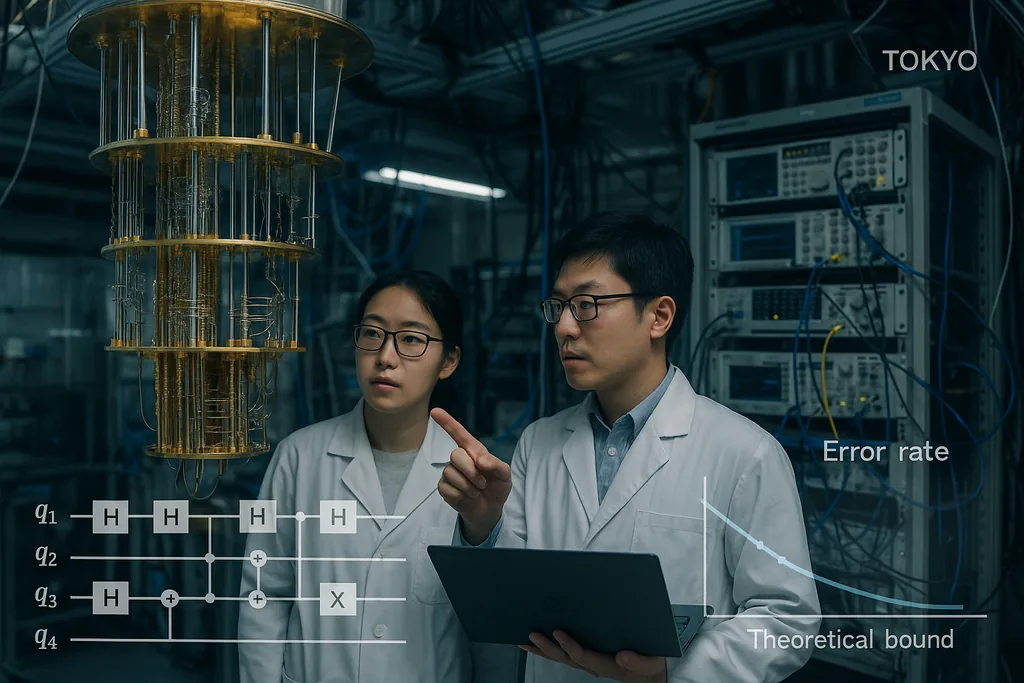

El 30 de septiembre de 2025, un equipo en Tokio publicó un artículo que presenta códigos de corrección de errores cuánticos que se acercan de manera inusual al límite teórico histórico para la comunicación y computación cuántica fiable —el denominado límite de hashing— manteniendo al mismo tiempo una decodificación eficiente. El resultado, ahora destacado en informes institucionales, no es una solución mágica de una sola línea; es un rediseño cuidadoso de las construcciones de comprobación de paridad de baja densidad y sus decodificadores que, en conjunto, reducen las tasas de error de trama a niveles prácticos y mantienen bajo el gasto computacional. Esas dos características —un rendimiento cercano a la capacidad y un coste de decodificación que escala linealmente con la máquina— son precisamente las propiedades necesarias para que los procesadores cuánticos pasen de ser curiosidades de laboratorio a máquinas capaces de abordar problemas reales en química, criptografía y ciencia climática.

Un código de capacidad casi óptima para el canal cuántico ruidoso

El límite de hashing es un techo teórico de la información: marca la tasa más alta a la que la información cuántica puede transmitirse de forma fiable a través de un canal ruidoso utilizando una codificación y decodificación óptimas. Históricamente, los códigos cuánticos cuya eficiencia es demostrable han estado lejos de ese límite o han requerido decodificadores impracticablemente pesados. Al demostrar códigos que se acercan al límite y que pueden decodificarse con recursos clásicos que escalan de forma modesta, Komoto y Kasai presentan un argumento convincente de que el escalado del hardware —el proyecto de conectar millones de cúbits físicos para generar muchos cúbits lógicos— es un objetivo de ingeniería realista en lugar de una quimera teórica.

Decodificadores: el cuello de botella ignorado que empieza a ser un problema resuelto

Los códigos de corrección de errores son solo la mitad de la historia; los decodificadores rápidos y precisos son la otra mitad. Durante el último año, varios avances algorítmicos han ido reduciendo el cuello de botella de la decodificación. En junio de 2025, unos investigadores describieron PLANAR, un algoritmo de decodificación exacta para ciertas topologías de código que convierte un problema de decodificación de máxima verosimilitud aparentemente intratable en un cálculo de función de partición de vidrio de espín eficientemente resoluble en grafos planares. Al aplicarse a datos experimentales, PLANAR redujo significativamente las tasas de error lógico y demostró que parte de lo que parecían límites del hardware era en realidad un decodificador subóptimo. Esa percepción es importante porque significa que mejores decodificadores pueden extraer más rendimiento de los dispositivos existentes sin necesidad de realizar cambios en el hardware cuántico.

En el extremo de la ingeniería, los equipos de la industria están trasladando estas ideas de decodificación a hardware clásico en tiempo real. IBM informó recientemente que un algoritmo clave de corrección de errores puede ejecutarse en FPGAs de AMD convencionales con la rapidez suficiente para proporcionar retroalimentación en tiempo real en sistemas superconductores, demostrando un funcionamiento que supera con creces la velocidad necesaria para muchas arquitecturas. Ejecutar decodificadores en chips clásicos accesibles es un paso crucial: transforma la corrección de errores de un proceso de software costoso y fuera de línea en un servicio práctico de baja latencia que puede integrarse en las pilas de control de grandes máquinas. Junto con los códigos de capacidad casi óptima, los decodificadores de hardware rápidos cierran el círculo entre la teoría y los sistemas desplegables.

Qué significa esta convergencia para las aplicaciones reales

Las aplicaciones cuánticas que prometen un valor transformador —simulación molecular para el descubrimiento de fármacos, optimización logística o nuevas primitivas criptográficas— suelen requerir millones de cúbits lógicos o tasas de error lógico extremadamente bajas mantenidas durante computaciones prolongadas. Hasta ahora, esas estimaciones de recursos se traducían en recuentos astronómicos de cúbits físicos porque la corrección de errores tenía umbrales deficientes y decodificadores costosos. La combinación de las construcciones de codificación de Komoto y Kasai, decodificadores mejorados como PLANAR y el impulso para ejecutar la decodificación en hardware clásico estándar reduce sustancialmente ese gasto de recursos en principio. Esto cambia el equilibrio: una generación de hardware cuántico que antes se consideraba impracticable podría estar ahora al alcance si los equipos de ingeniería logran entregar matrices de cúbits de escala moderada con las fidelidades físicas esperadas.

Ya existen líneas orientadas a aplicaciones que se basan en este trabajo. Por ejemplo, investigadores que exploran el aprendizaje automático cuántico han demostrado que una corrección de errores parcial o aproximada puede hacer que los modelos cuánticos a corto plazo sean mucho más prácticos que antes, reduciendo las demandas de hardware necesarias para observar una ventaja. Tales sinergias entre la teoría de códigos, la tolerancia a fallos aproximada y el diseño de algoritmos podrían acelerar los usos prácticos en máquinas intermedias incluso antes de que llegue la tolerancia a fallos completa.

Barreras pendientes

A pesar de los progresos, persisten varios problemas complejos de ingeniería y física. Los códigos y decodificadores del artículo de Komoto–Kasai se demuestran en simulaciones y estudios numéricos; trasladarlos al silicio, a circuitos superconductores, a iones atrapados o a configuraciones fotónicas requiere diseñar cadenas de decodificación con garantías extremas de tiempo real, enrutar millones de señales a través de estructuras criogénicas y suprimir efectos raros pero devastadores como los errores correlacionados inducidos por rayos cósmicos. Implementar aritmética de campos finitos no binarios en hardware, integrar la extracción de síndromes sin añadir ruido y validar el rendimiento en modelos de ruido de dispositivos realistas son tareas no triviales que determinarán si la promesa numérica se convierte en una realidad operativa.

También existen estrategias de hardware competidoras en juego. Algunos grupos están mejorando la resiliencia intrínseca al error del hardware —por ejemplo, los enfoques fotónicos y de cúbits de gato (cat-qubits) prometen diferentes equilibrios entre los sesgos de ruido naturales y el recuento de recursos— y las comparativas entre estas arquitecturas serán esenciales a medida que los decodificadores escalables estén disponibles. No todas las arquitecturas podrán explotar cada código o decodificador de la misma manera, por lo que la comunidad aún necesita una validación multiplataforma.

De la teoría a la ingeniería: los próximos pasos

El camino a seguir parece un programa coordinado de tres vías. Primero, los diseñadores de códigos perfeccionarán las construcciones para manejar modelos de ruido más realistas y errores correlacionados, y para reducir aún más los suelos de error. Segundo, los equipos de decodificadores continuarán reduciendo la latencia y el coste energético, y portarán los algoritmos a FPGAs, ASICs y lógica criogénica donde sea necesario. Terc, los grupos de hardware evaluarán los códigos y decodificadores en dispositivos reales, informando no solo de las tasas de error lógico, sino también de los costes de infraestructura ocultos: computación clásica, cableado, refrigeración y mantenimiento. Si estas tres vías convergen, la comunidad podrá convertir la promesa abstracta de la ventaja cuántica en hojas de ruta concretas para máquinas que realicen un trabajo útil.

En resumen, el trabajo reciente sobre los códigos LDPC cercanos al límite de hashing no es un triunfo aislado, sino la señal más reciente y convincente de que una combinación de códigos más inteligentes, mejores decodificadores e integración práctica de hardware clásico puede cerrar la brecha entre la teoría y la aplicación. El cronograma para una computación cuántica ampliamente útil sigue siendo incierto, pero estos avances mejoran materialmente el argumento de ingeniería para construir la próxima generación de máquinas que intentarán realizar un trabajo real para la industria y la ciencia.

Fuentes

- npj Quantum Information (Komoto & Kasai: "Quantum error correction near the coding theoretical bound").

- Physical Review Letters (Cao et al.: "Exact Decoding of Quantum Error‑Correcting Codes").

- Materiales de prensa del Institute of Science Tokyo que resumen el trabajo de Komoto & Kasai.

- Divulgaciones e informes de investigación de IBM sobre implementaciones de decodificadores cuánticos en FPGA.

Comments

No comments yet. Be the first!