Neue Codes reduzieren das Rauschen, das Quantencomputer am Skalieren hindert

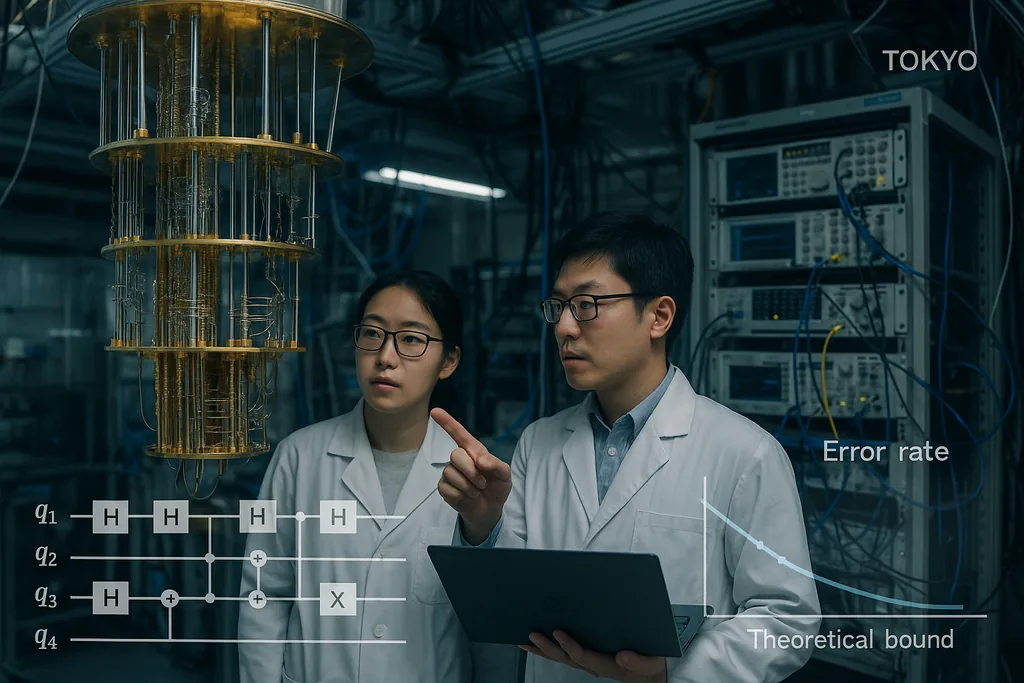

Am 30. September 2025 veröffentlichte ein Team in Tokio eine Arbeit, die Quantenfehlerkorrektur-Codes vorstellt, die der langjährigen theoretischen Grenze für zuverlässige Quantenkommunikation und -berechnung – der sogenannten Hashing-Grenze – ungewöhnlich nahe kommen und dabei effizient dekodierbar bleiben. Das Ergebnis, das nun in institutionellen Berichten hervorgehoben wird, ist keine einfache Patentlösung; es ist eine sorgfältige Neugestaltung von Low-Density-Parity-Check-Konstruktionen (LDPC) und deren Decodern, die zusammen die Rahmenfehlerraten auf ein praktisches Niveau senken und den Rechenaufwand niedrig halten. Diese beiden Merkmale – eine Leistung nahe der Kapazitätsgrenze und Dekodierungskosten, die linear mit der Maschine skalieren – sind genau die Eigenschaften, die erforderlich sind, um Quantenprozessoren von Laborkuriositäten zu Maschinen zu entwickeln, die reale Probleme in der Chemie, Kryptographie und Klimawissenschaft lösen können.

Ein Code nahe der Kapazitätsgrenze für den verrauschten Quantenkanal

Die Hashing-Grenze ist eine informationstheoretische Obergrenze: Sie markiert die höchste Rate, mit der Quanteninformationen unter Verwendung optimaler Kodierung und Dekodierung zuverlässig über einen verrauschten Kanal übertragen werden können. Historisch gesehen waren Quantencodes, die nachweislich effizient sind, weit von dieser Grenze entfernt oder erforderten unpraktisch komplexe Decoder. Durch den Nachweis von Codes, die sich sowohl der Grenze nähern als auch mit moderat skalierenden klassischen Ressourcen dekodiert werden können, liefern Komoto und Kasai ein überzeugendes Argument dafür, dass die Hardware-Skalierung – das Projekt, Millionen physikalischer Qubits zu verschalten, um viele logische Qubits zu erhalten – ein realistisches technisches Ziel und kein theoretischer Wunschtraum ist.

Decoder: Der unbeachtete Flaschenhals wird zum gelösten Problem

Fehlerkorrigierende Codes sind nur die halbe Miete; schnelle, präzise Decoder sind die andere Hälfte. Im vergangenen Jahr haben mehrere algorithmische Fortschritte den Dekodierungs-Flaschenhals verkleinert. Im Juni 2025 beschrieben Forscher PLANAR, einen exakten Dekodierungsalgorithmus für bestimmte Code-Topologien, der ein scheinbar unlösbares Maximum-Likelihood-Dekodierungsproblem in eine effizient lösbare Spin-Glas-Zustandssummen-Berechnung auf planaren Graphen verwandelt. Bei der Anwendung auf experimentelle Daten reduzierte PLANAR die logischen Fehlerraten erheblich und zeigte, dass ein Teil dessen, was nach Hardware-Limits aussah, tatsächlich auf einen suboptimalen Decoder zurückzuführen war. Diese Erkenntnis ist wichtig, da sie bedeutet, dass bessere Decoder mehr Leistung aus bestehenden Geräten herausholen können, ohne dass die Quantenhardware geändert werden muss.

Auf der technischen Seite überführen Industrieteams diese Dekodierungsideen in Echtzeit-Hardware. IBM berichtete kürzlich, dass ein wichtiger Fehlerkorrektur-Algorithmus auf herkömmlichen AMD-FPGAs schnell genug für Echtzeit-Feedback in supraleitenden Systemen laufen kann, was einen Betrieb weit über der für viele Architekturen erforderlichen Geschwindigkeit demonstriert. Das Ausführen von Decodern auf zugänglichen klassischen Chips ist ein entscheidender Schritt: Es verwandelt die Fehlerkorrektur von einem Offline-Softwareprozess in einen praktischen Dienst mit geringer Latenz, der in die Kontroll-Stacks großer Maschinen eingebettet werden kann. Zusammen mit den Codes nahe der Kapazitätsgrenze schließen schnelle Hardware-Decoder die Lücke zwischen Theorie und einsatzfähigen Systemen.

Was diese Konvergenz für reale Anwendungen bedeutet

Quantenanwendungen, die einen transformativen Wert versprechen – Molekularsimulationen für die Wirkstoffforschung, Optimierung für die Logistik oder neue kryptographische Primitive – erfordern typischerweise Millionen von logischen Qubits oder extrem niedrige logische Fehlerraten über lange Berechnungen hinweg. Bisher bedeuteten diese Ressourcenschätzungen astronomische Zahlen an physikalischen Qubits, da die Fehlerkorrektur sowohl schlechte Schwellenwerte als auch kostspielige Decoder aufwies. Die Kombination aus den Kodierungskonstruktionen von Komoto und Kasai, verbesserten Decodern wie PLANAR und dem Vorstoß, die Dekodierung auf standardmäßiger klassischer Hardware auszuführen, senkt diesen Overhead im Prinzip erheblich. Dies verschiebt das Gleichgewicht: Eine Generation von Quantenhardware, die zuvor als unpraktisch galt, könnte nun in Reichweite sein, wenn Ingenieurteams Arrays mit moderater Qubit-Anzahl und den erwarteten physikalischen Fidelitäten liefern können.

Es gibt bereits anwendungsorientierte Ansätze, die auf dieser Arbeit aufbauen. Forscher, die sich mit Quanten-Maschinellem-Lernen befassen, haben beispielsweise gezeigt, dass eine teilweise oder ungefähre Fehlerkorrektur kurzfristige Quantenmodelle weitaus praktischer machen kann als bisher, was die Hardwareanforderungen für einen Quantenvorteil reduziert. Solche Synergien zwischen Kodierungstheorie, approximativer Fehlertoleranz und Algorithmen-Design könnten die praktischen Anwendungen auf intermediären Maschinen beschleunigen, noch bevor die vollständige Fehlertoleranz erreicht ist.

Verbleibende Barrieren

Trotz der Fortschritte bleiben mehrere schwierige Probleme in Technik und Physik bestehen. Die Codes und Decoder im Papier von Komoto und Kasai wurden in Simulationen und numerischen Studien nachgewiesen; sie in Silizium, supraleitende Schaltkreise, gefangene Ionen oder photonische Setups zu übertragen, erfordert die Entwicklung von Decoder-Pipelines mit extremen Echtzeitgarantien, das Routing von Millionen von Signalen durch kryogene Stacks und die Unterdrückung seltener, aber verheerender Effekte wie durch kosmische Strahlung induzierte korrelierte Fehler. Die Implementierung nicht-binärer Arithmetik in endlichen Körpern in Hardware, die Integration der Syndrom-Extraktion ohne zusätzliches Rauschen und die Validierung der Leistung in realistischen Rauschmodellen sind nicht triviale Aufgaben, die entscheiden werden, ob das numerische Versprechen zu einer betrieblichen Realität wird.

Es sind auch konkurrierende Hardware-Strategien im Spiel. Einige Gruppen verbessern die intrinsische Fehlertoleranz der Hardware – beispielsweise beanspruchen photonische und Cat-Qubit-Ansätze unterschiedliche Kompromisse zwischen natürlichen Rausch-Biases und Ressourcenzahlen –, und das Benchmarking zwischen diesen Architekturen wird mit der Verfügbarkeit skalierbarer Decoder unerlässlich sein. Nicht jede Architektur wird in der Lage sein, jeden Code oder Decoder gleichermaßen gut zu nutzen, sodass die Community weiterhin plattformübergreifende Validierungen benötigt.

Von der Theorie zum Engineering: Die nächsten Schritte

Der Weg nach vorn gleicht einem koordinierten Drei-Säulen-Programm. Erstens werden Code-Designer die Konstruktionen verfeinern, um realistischere Rauschmodelle und korrelierte Fehler zu bewältigen und die Error-Floors weiter zu senken. Zweitens werden Decoder-Teams weiterhin die Latenz und die Energiekosten senken und Algorithmen bei Bedarf auf FPGAs, ASICs und kryogene Logik portieren. Drittens werden Hardware-Gruppen Codes und Decoder auf echten Geräten benchmarken und dabei nicht nur logische Fehlerraten, sondern auch die versteckten Infrastrukturkosten melden: klassische Rechenleistung, Verkabelung, Kühlung und Wartung. Wenn diese drei Wege konvergieren, wird die Community in der Lage sein, das abstrakte Versprechen des Quantenvorteils in konkrete Roadmaps für Maschinen zu verwandeln, die nützliche Arbeit leisten.

Kurz gesagt, die jüngste Arbeit an LDPC-Codes nahe der Hashing-Grenze ist kein isolierter Triumph, sondern das jüngste, überzeugende Zeichen dafür, dass eine Kombination aus intelligenteren Codes, besseren Decodern und praktischer Integration klassischer Hardware die Lücke zwischen Theorie und Anwendung schließen kann. Der Zeitplan für breit nutzbares Quantencomputing bleibt ungewiss, aber diese Fortschritte verbessern die technischen Voraussetzungen für den Bau der nächsten Generation von Maschinen, die versuchen werden, reale Aufgaben für Industrie und Wissenschaft zu lösen.

Quellen

- npj Quantum Information (Komoto & Kasai: "Quantum error correction near the coding theoretical bound").

- Physical Review Letters (Cao et al.: "Exact Decoding of Quantum Error‑Correcting Codes").

- Pressematerialien des Institute of Science Tokyo, die die Arbeit von Komoto & Kasai zusammenfassen.

- IBM Research-Offenlegungen und Berichte über FPGA-Implementierungen von Quanten-Decodern.

Kommentare

Noch keine Kommentare. Seien Sie der Erste!