Novos códigos reduzem o ruído que impede o escalonamento dos computadores quânticos

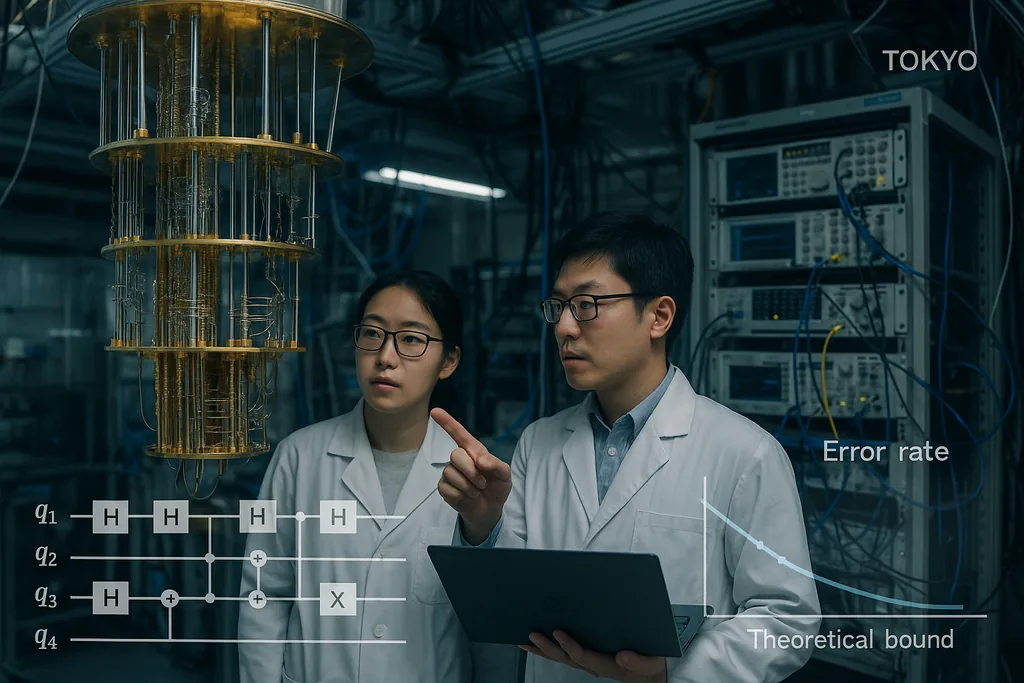

Em 30 de setembro de 2025, uma equipe em Tóquio publicou um artigo apresentando códigos de correção de erros quânticos que se aproximam excepcionalmente do limite teórico de longa data para a comunicação e computação quântica confiável — o chamado limite de hashing (hashing bound) — ao mesmo tempo em que permanecem eficientemente decodificáveis. O resultado, agora destacado em relatórios institucionais, não é uma solução mágica de uma única linha; é um redesenho cuidadoso de construções de verificação de paridade de baixa densidade (LDPC) e de seus decodificadores que, juntos, reduzem as taxas de erro de quadro para níveis práticos e mantêm o overhead computacional baixo. Essas duas características — desempenho próximo da capacidade e custo de decodificação que escala linearmente com a máquina — são as propriedades exatas necessárias para mover os processadores quânticos de curiosidades laboratoriais para máquinas que possam enfrentar problemas reais em química, criptografia e ciência climática.

Um código próximo da capacidade para o canal quântico ruidoso

O limite de hashing é um teto da teoria da informação: ele marca a taxa mais alta na qual a informação quântica pode ser transmitida de forma confiável através de um canal ruidoso ao usar codificação e decodificação ideais. Historicamente, os códigos quânticos comprovadamente eficientes estiveram longe desse limite ou exigiram decodificadores impraticavelmente pesados. Ao demonstrar códigos que tanto se aproximam do limite quanto podem ser decodificados com recursos clássicos que escalam modestamente, Komoto e Kasai apresentam um argumento convincente de que o escalonamento de hardware — o projeto de conectar milhões de qubits físicos para gerar muitos qubits lógicos — é uma meta de engenharia realista, em vez de um sonho teórico distante.

Decodificadores: o gargalo oculto tornando-se um problema resolvido

Códigos de correção de erros são apenas metade da história; decodificadores rápidos e precisos são a outra metade. Ao longo do último ano, vários avanços algorítmicos reduziram o gargalo da decodificação. Em junho de 2025, pesquisadores descreveram o PLANAR, um algoritmo de decodificação exata para certas topologias de código que transforma um problema de decodificação de máxima verossimilhança, aparentemente intratável, em um cálculo de função de partição de vidro de spin eficientemente resolvível em grafos planares. Quando aplicado a dados experimentais, o PLANAR reduziu significativamente as taxas de erro lógico e mostrou que parte do que parecia ser limitações de hardware era, na verdade, um decodificador subótimo. Essa percepção é importante porque significa que decodificadores melhores podem extrair mais desempenho dos dispositivos existentes sem qualquer alteração no hardware quântico.

Na vertente da engenharia, equipes da indústria estão transferindo essas ideias de decodificação para hardware clássico em tempo real. A IBM informou recentemente que um algoritmo fundamental de correção de erros pode ser executado em FPGAs convencionais da AMD com velocidade suficiente para feedback em tempo real em sistemas supercondutores, demonstrando uma operação bem além da velocidade necessária para muitas arquiteturas. Executar decodificadores em chips clássicos acessíveis é um passo crucial: transforma a correção de erros de um processo de software offline e dispendioso em um serviço prático de baixa latência que pode ser incorporado em pilhas de controle para grandes máquinas. Juntamente com os códigos de quase-capacidade, os decodificadores de hardware rápidos fecham o ciclo entre a teoria e os sistemas implantáveis.

O que essa convergência significa para aplicações reais

As aplicações quânticas que prometem valor transformador — simulação molecular para descoberta de fármacos, otimização para logística ou novas primitivas criptográficas — normalmente exigem milhões de qubits lógicos ou taxas de erro lógico extremamente baixas sustentadas em computações longas. Até agora, essas estimativas de recursos se traduziam em contagens astronômicas de qubits físicos porque a correção de erros possuía limiares ruins e decodificadores caros. A combinação das construções de codificação de Komoto e Kasai, decodificadores aprimorados como o PLANAR e o esforço para executar a decodificação em hardware clássico padrão reduz substancialmente esse overhead em princípio. Isso altera o equilíbrio: uma geração de hardware quântico que anteriormente era julgada impraticável pode agora estar ao alcance se as equipes de engenharia conseguirem entregar matrizes de qubits de escala moderada com as fidelidades físicas esperadas.

Já existem vertentes orientadas a aplicações baseadas neste trabalho. Por exemplo, pesquisadores que exploram o aprendizado de máquina quântico mostraram que a correção de erros parcial ou aproximada pode tornar os modelos quânticos de curto prazo muito mais práticos do que antes, reduzindo as demandas de hardware necessárias para observar uma vantagem. Tais sinergias entre a teoria da codificação, a tolerância a falhas aproximada e o design de algoritmos poderiam acelerar usos práticos em máquinas intermediárias antes mesmo da chegada da tolerância a falhas completa.

Barreiras que permanecem

Apesar do progresso, vários problemas difíceis de engenharia e física permanecem. Os códigos e decodificadores no artigo de Komoto–Kasai são demonstrados em simulações e estudos numéricos; movê-los para silício, circuitos supercondutores, íons aprisionados ou configurações fotônicas exige a engenharia de pipelines de decodificadores com garantias extremas de tempo real, o roteamento de milhões de sinais através de pilhas criogênicas e a supressão de efeitos raros, mas devastadores, como erros correlacionados induzidos por raios cósmicos. Implementar aritmética de campos finitos não binários em hardware, integrar a extração de síndrome sem adicionar ruído e validar o desempenho em modelos realistas de ruído de dispositivos são tarefas não triviais que determinarão se a promessa numérica se tornará uma realidade operacional.

Há também estratégias de hardware concorrentes em jogo. Alguns grupos estão melhorando a resiliência intrínseca ao erro do hardware — por exemplo, abordagens fotônicas e de cat-qubits alegam diferentes compensações entre vieses de ruído naturais e contagem de recursos — e o benchmarking entre essas arquiteturas será essencial à medida que decodificadores escalonáveis se tornarem disponíveis. Nem toda arquitetura será capaz de explorar cada código ou decodificador igualmente bem, portanto, a comunidade ainda precisa de validação multiplataforma.

Da teoria à engenharia: os próximos passos

O caminho a seguir assemelha-se a um programa coordenado em três frentes. Primeiro, os designers de códigos refinarão as construções para lidar com modelos de ruído mais realistas e erros correlacionados, e para reduzir ainda mais os pisos de erro. Segundo, as equipes de decodificadores continuarão a reduzir a latência e o custo de energia e a portar algoritmos para FPGAs, ASICs e lógica criogênica onde for necessário. Terceiro, os grupos de hardware farão o benchmarking de códigos e decodificadores em dispositivos reais, relatando não apenas as taxas de erro lógico, mas também os custos ocultos de infraestrutura: computação clássica, cabeamento, resfriamento e manutenção. Se essas três frentes convergirem, a comunidade será capaz de transformar a promessa abstrata da vantagem quântica em roteiros concretos para máquinas que realizam trabalho útil.

Em suma, o trabalho recente em códigos LDPC próximos ao limite de hashing não é um triunfo isolado, mas o sinal mais recente e convincente de que uma combinação de códigos mais inteligentes, decodificadores melhores e integração prática de hardware clássico pode fechar a lacuna entre a teoria e a aplicação. O cronograma para uma computação quântica amplamente útil permanece incerto, mas esses avanços melhoram materialmente o argumento de engenharia para a construção da próxima geração de máquinas que tentarão realizar trabalho real para a indústria e a ciência.

Fontes

- npj Quantum Information (Komoto & Kasai: "Quantum error correction near the coding theoretical bound").

- Physical Review Letters (Cao et al.: "Exact Decoding of Quantum Error‑Correcting Codes").

- Materiais de imprensa do Institute of Science Tokyo resumindo o trabalho de Komoto & Kasai.

- Divulgações e relatórios de pesquisa da IBM sobre implementações em FPGA de decodificadores quânticos.

Comments

No comments yet. Be the first!