De nouveaux codes réduisent le bruit qui empêche le passage à l'échelle des ordinateurs quantiques

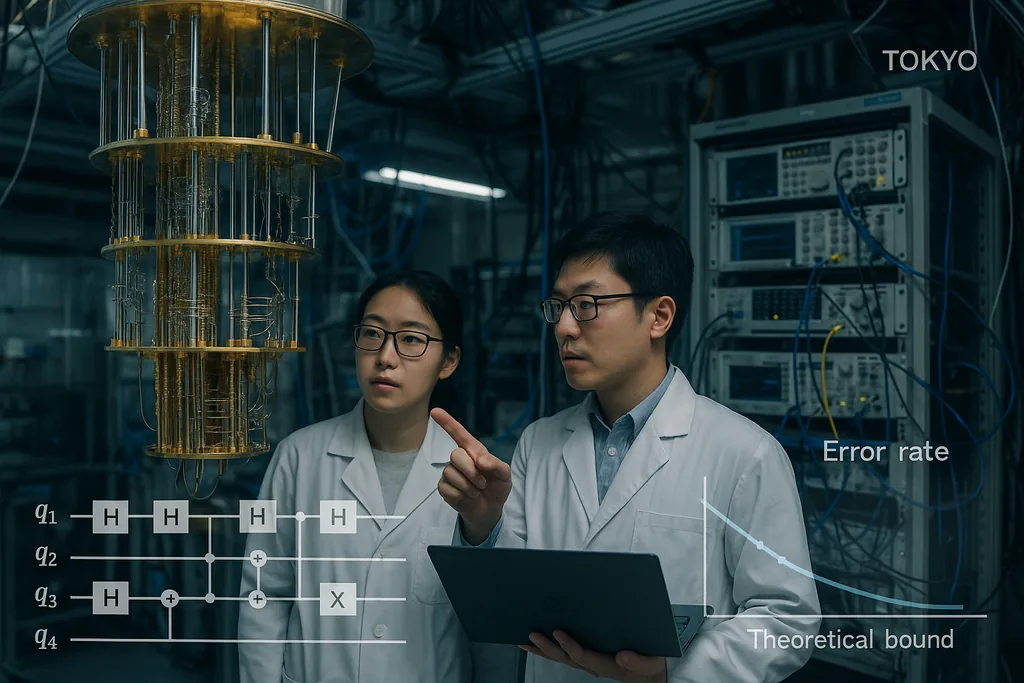

Le 30 septembre 2025, une équipe à Tokyo a publié un article présentant des codes de correction d'erreurs quantiques qui se rapprochent de manière inhabituelle de la limite théorique de longue date pour une communication et un calcul quantiques fiables — ce que l'on appelle la limite de hachage (hashing bound) — tout en restant efficacement décodables. Le résultat, désormais mis en avant dans des communiqués institutionnels, n'est pas une solution miracle en une ligne ; il s'agit d'une refonte minutieuse des constructions de codes LDPC (low-density parity-check) et de leurs décodeurs qui, ensemble, ramènent les taux d'erreur de trame à des niveaux pratiques et maintiennent un surcoût de calcul faible. Ces deux caractéristiques — une performance proche de la capacité et un coût de décodage qui évolue linéairement avec la machine — sont précisément les propriétés nécessaires pour faire passer les processeurs quantiques du stade de curiosités de laboratoire à celui de machines capables de s'attaquer à des problèmes réels en chimie, en cryptographie et en science du climat.

Un code proche de la capacité pour le canal quantique bruité

La limite de hachage est un plafond de la théorie de l'information : elle marque le taux le plus élevé auquel l'information quantique peut être transmise de manière fiable à travers un canal bruité en utilisant un codage et un décodage optimaux. Historiquement, les codes quantiques dont l'efficacité est prouvée étaient loin de cette limite ou nécessitaient des décodeurs impraticables car trop lourds. En démontrant des codes qui à la fois s'approchent de la limite et peuvent être décodés avec des ressources classiques à l'échelle modeste, Komoto et Kasai avancent un argument convaincant selon lequel le passage à l'échelle du matériel — le projet de câbler des millions de qubits physiques pour obtenir de nombreux qubits logiques — est un objectif d'ingénierie réaliste plutôt qu'une chimère théorique.

Décodeurs : le goulot d'étranglement méconnu en passe d'être résolu

Les codes de correction d'erreurs ne représentent que la moitié de l'histoire ; des décodeurs rapides et précis constituent l'autre moitié. Au cours de l'année écoulée, plusieurs avancées algorithmiques ont réduit ce goulot d'étranglement du décodage. En juin 2025, des chercheurs ont décrit PLANAR, un algorithme de décodage exact pour certaines topologies de codes qui transforme un problème de décodage par maximum de vraisemblance apparemment insoluble en un calcul de fonction de partition de verre de spin efficacement résoluble sur des graphes planaires. Appliqué à des données expérimentales, PLANAR a réduit de manière significative les taux d'erreur logique et a montré qu'une partie de ce qui ressemblait à des limites matérielles provenait en réalité d'un décodeur sous-optimal. Cette observation est importante car elle signifie que de meilleurs décodeurs peuvent extraire davantage de performance des dispositifs existants sans aucune modification du matériel quantique.

Sur le plan de l'ingénierie, les équipes industrielles intègrent ces concepts de décodage dans du matériel classique en temps réel. IBM a récemment rapporté qu'un algorithme clé de correction d'erreurs peut fonctionner sur des FPGA AMD conventionnels assez rapidement pour permettre un retour d'information en temps réel dans les systèmes supraconducteurs, démontrant un fonctionnement bien au-delà de la vitesse requise pour de nombreuses architectures. L'exécution de décodeurs sur des puces classiques accessibles est une étape cruciale : elle transforme la correction d'erreurs, d'un processus logiciel hors ligne et coûteux, en un service pratique à faible latence qui peut être intégré dans les piles de contrôle des grandes machines. Associés aux codes proches de la capacité, les décodeurs matériels rapides bouclent la boucle entre la théorie et les systèmes déployables.

Ce que cette convergence signifie pour les applications réelles

Les applications quantiques qui promettent une valeur transformative — simulation moléculaire pour la découverte de médicaments, optimisation pour la logistique ou nouvelles primitives cryptographiques — nécessitent généralement des millions de qubits logiques ou des taux d'erreur logique extrêmement bas maintenus sur de longs calculs. Jusqu'à présent, ces estimations de ressources se traduisaient par des nombres astronomiques de qubits physiques, car la correction d'erreurs présentait à la fois des seuils médiocres et des décodeurs coûteux. La combinaison des constructions de codage de Komoto et Kasai, des décodeurs améliorés tels que PLANAR et de la volonté d'exécuter le décodage sur du matériel classique standard réduit considérablement ce surcoût en principe. Cela modifie l'équilibre : une génération de matériel quantique auparavant jugée irréalisable pourrait désormais être à portée de main si les équipes d'ingénierie parviennent à produire des réseaux de qubits à échelle modérée avec les fidélités physiques attendues.

Des axes orientés vers les applications s'appuient déjà sur ces travaux. Par exemple, des chercheurs explorant l'apprentissage automatique quantique ont montré qu'une correction d'erreurs partielle ou approximative peut rendre les modèles quantiques à court terme bien plus pratiques qu'auparavant, réduisant les exigences matérielles nécessaires pour constater un avantage. De telles synergies entre la théorie du codage, la tolérance aux pannes approximative et la conception d'algorithmes pourraient accélérer les utilisations pratiques sur des machines intermédiaires avant même l'arrivée d'une tolérance aux pannes complète.

Les obstacles subsistants

Malgré les progrès, plusieurs problèmes complexes d'ingénierie et de physique subsistent. Les codes et décodeurs de l'article de Komoto-Kasai sont démontrés dans des simulations et des études numériques ; les transposer dans le silicium, les circuits supraconducteurs, les ions piégés ou les configurations photoniques nécessite de concevoir des pipelines de décodeurs avec des garanties extrêmes de temps réel, d'acheminer des millions de signaux à travers des structures cryogéniques et de supprimer des effets rares mais dévastateurs tels que les erreurs corrélées induites par les rayons cosmiques. L'implémentation de l'arithmétique de corps fini non binaire dans le matériel, l'intégration de l'extraction de syndrome sans ajouter de bruit et la validation des performances dans des modèles de bruit de dispositif réalistes sont des tâches non triviales qui détermineront si la promesse numérique devient une réalité opérationnelle.

Des stratégies matérielles concurrentes sont également en jeu. Certains groupes améliorent la résilience intrinsèque aux erreurs du matériel — par exemple, les approches photoniques et à qubits de chat (cat-qubit) revendiquent différents compromis entre les biais de bruit naturel et le nombre de ressources — et l'analyse comparative (benchmarking) entre ces architectures sera essentielle à mesure que des décodeurs évolutifs deviendront disponibles. Toutes les architectures ne pourront pas exploiter chaque code ou décodeur aussi bien, la communauté a donc encore besoin d'une validation multiplateforme.

De la théorie à l'ingénierie : les prochaines étapes

La voie à suivre ressemble à un programme coordonné sur trois axes. Premièrement, les concepteurs de codes affineront les constructions pour gérer des modèles de bruit plus réalistes et des erreurs corrélées, et pour abaisser davantage les planchers d'erreur. Deuxièmement, les équipes chargées des décodeurs continueront de réduire la latence et le coût énergétique, et de porter les algorithmes sur des FPGA, des ASIC et de la logique cryogénique si nécessaire. Troisièmement, les groupes de matériel évalueront les codes et les décodeurs sur des dispositifs réels, en signalant non seulement les taux d'erreur logique mais aussi les coûts d'infrastructure cachés : calcul classique, câblage, refroidissement et maintenance. Si ces trois axes convergent, la communauté pourra transformer la promesse abstraite de l'avantage quantique en feuilles de route concrètes pour des machines effectuant un travail utile.

En résumé, les récents travaux sur les codes LDPC proches de la limite de hachage ne sont pas un triomphe isolé, mais le dernier signe convaincant qu'une combinaison de codes plus intelligents, de meilleurs décodeurs et d'une intégration pratique du matériel classique peut combler l'écart entre la théorie et l'application. Le calendrier pour une informatique quantique largement utile reste incertain, mais ces avancées améliorent concrètement les arguments d'ingénierie en faveur de la construction de la prochaine génération de machines qui tenteront d'accomplir un travail réel pour l'industrie et la science.

Sources

- npj Quantum Information (Komoto & Kasai : « Quantum error correction near the coding theoretical bound »).

- Physical Review Letters (Cao et al. : « Exact Decoding of Quantum Error‑Correcting Codes »).

- Documents de presse de l'Institute of Science Tokyo résumant les travaux de Komoto & Kasai.

- Divulgations et rapports de recherche d'IBM sur les implémentations FPGA de décodeurs quantiques.

Comments

No comments yet. Be the first!