新编码削减了阻碍量子计算机规模化的噪声

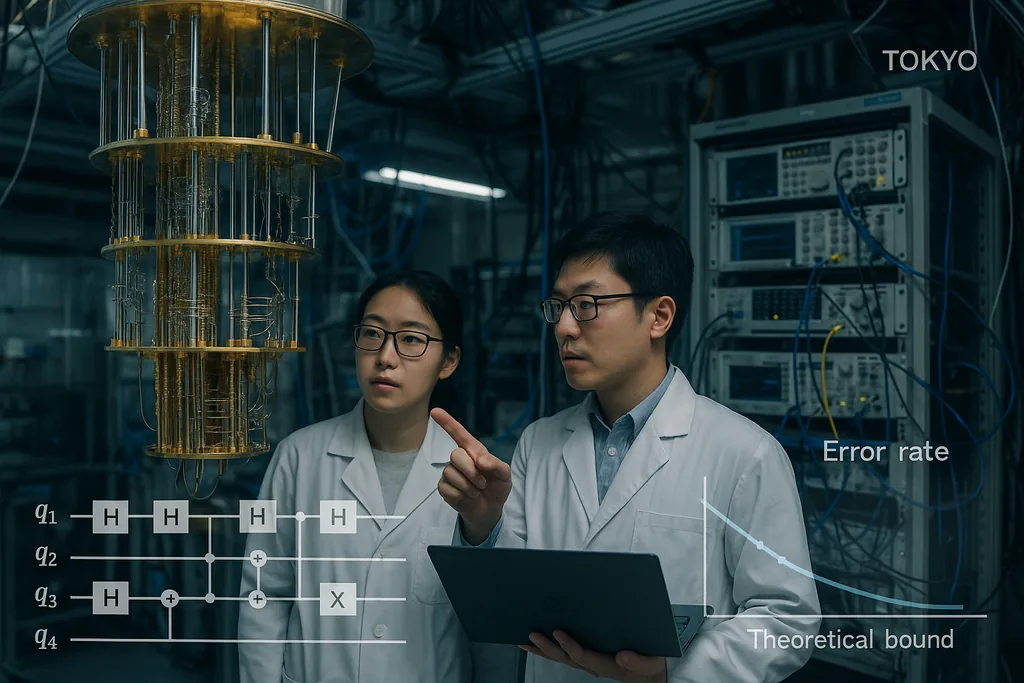

2025年9月30日,Tokyo 的一个团队发表了一篇论文,展示了量子纠错码在保持高效可译码性的同时,异常接近长期存在的可靠量子通信与计算理论极限——即所谓的 hashing bound(散列界)。这一研究结果目前已在机构报告中得到重点介绍,它并非某种一蹴而就的魔法,而是对低密度奇偶校验(LDPC)结构及其译码器的精细重新设计,共同将帧错误率降低到实用水平,并保持了较低的计算开销。这两个特性——接近信道容量的性能和随机器线性扩展的译码成本——正是将量子处理器从实验室中的奇趣装置转变为能够解决化学、密码学和气候科学中实际问题的机器所必需的属性。

接近有噪量子信道容量的编码

hashing bound 是一个信息论上限:它标志着在使用最优编码和译码时,通过有噪信道可靠传输量子信息的最高速率。从历史上看,可证明高效的量子编码要么远离该极限,要么需要实际操作中难以实现的沉重译码器。通过展示既能接近该界限,又能在适度规模的经典资源下完成译码的编码,Komoto 和 Kasai 有力地证明了硬件规模化——即连接数百万个物理量子比特(physical qubits)以产生大量逻辑量子比特(logical qubits)的项目——是一个现实的工程目标,而非理论上的幻想。

译码器:正在被攻克的幕后瓶颈

纠错码只是故事的一半,快速且准确的译码器是另一半。在过去的一年里,几项算法进展逐渐攻克了译码瓶颈。2025年6月,研究人员描述了 PLANAR,这是一种针对特定编码拓扑的精确译码算法,它将看似棘手的极大似然译码问题转化为平面图上可高效求解的自旋玻璃配分函数计算。当应用于实验数据时,PLANAR 显著降低了逻辑错误率,并表明部分看起来像是硬件限制的因素实际上源于次优的译码器。这一洞察至关重要,因为它意味着更好的译码器可以在不改变量子硬件的情况下,从现有设备中挤出更多性能。

在工程端,行业团队正在将这些译码构想转移到实时经典硬件中。IBM 最近报告称,一种关键的纠错算法可以在常规的 AMD FPGA 上运行,其速度足以实现超导系统中的实时反馈,展示了远超许多架构所需速度的运行能力。在通用的经典芯片上运行译码器是一个关键步骤:它将纠错从一个离线的、耗时的软件过程转变为一种实用的、低延迟的服务,可以嵌入到大型机器的控制栈中。结合接近信道容量的编码,快速硬件译码器闭合了理论与可部署系统之间的环路。

这种融合对实际应用的意义

有望带来变革性价值的量子应用——用于药物研发的分子模拟、物流优化或新的加密原语——通常需要数百万个逻辑量子比特,或者在长时间计算中维持极低的逻辑错误率。直到现在,这些资源估算往往会转化为天文数字般的物理量子比特数量,因为过去的纠错方案既有较差的阈值,又有昂贵的译码器。Komoto 和 Kasai 的编码结构、PLANAR 等改进的译码器,以及在标准经典硬件上运行译码的努力,从原则上显著降低了这种开销。这改变了天平的平衡:如果工程团队能够交付具有预期物理保真度(physical fidelities)的中等规模量子比特阵列,那么一代此前被认为不切实际的量子硬件现在可能已触手可及。

已经有基于这项工作的应用导向型研究在开展。例如,探索量子机器学习的研究人员表明,部分或近似纠错可以使近期的量子模型比以往任何时候都更具实用性,减少了实现优势所需的硬件需求。编码理论、近似容错与算法设计之间的这种协同作用,甚至可以在完全容错实现之前,加速中间代机器上的实际应用。

依然存在的障碍

尽管取得了进展,但仍存在若干艰巨的工程和物理问题。Komoto–Kasai 论文中的编码和译码器是在模拟和数值研究中展示的;将它们转移到硅、超导电路、陷阱离子或光子装置中,需要设计具有极高实时保障的译码流水线,引导数百万个信号通过低温堆栈,并抑制诸如宇宙射线诱导的相关错误等罕见但具有破坏性的影响。在硬件中实现非二进制有限域运算、在不引入噪声的情况下集成校验子提取(syndrome extraction),以及在现实的设备噪声模型中验证性能,都是决定数值上的前景能否转化为运行现实的非凡任务。

此外,还有相互竞争的硬件策略在发挥作用。一些团队正在提高硬件固有的错误抵御能力——例如,光子和 cat-qubit 方法声称在自然噪声偏置和资源计数之间有不同的权衡——随着可扩展译码器的出现,这些架构之间的基准测试将至关重要。并非每种架构都能同样好地利用每种编码或译码器,因此社区仍需要跨平台验证。

从理论到工程:下一步工作

前进之路看起来像是一个协调的三轨计划。首先,编码设计者将改进结构以处理更现实的噪声模型和相关错误,并进一步降低错误门限(error floors)。其次,译码器团队将继续降低延迟和能耗,并在必要时将算法移植到 FPGA、ASIC 和低温逻辑中。第三,硬件团队将在真实设备上对编码和译码器进行基准测试,不仅报告逻辑错误率,还报告隐藏的基础设施成本:经典计算、布线、冷却和维护。如果这三个轨道能汇合,社区将能够把量子优势的抽象承诺转化为能够从事有用工作的机器的具体路线图。

简而言之,最近关于接近 hashing bound 的 LDPC 编码的工作并非孤立的胜利,而是一个最新的、令人信服的信号,表明更智能的编码、更好的译码器和实用的经典硬件集成的结合,可以弥合理论与应用之间的差距。广泛通用的 quantum computing(量子计算)的时间表仍不确定,但这些进展实质上改进了构建下一代机器的工程可行性,这些机器将尝试为工业和科学完成实际工作。

Sources

- npj Quantum Information (Komoto & Kasai: "Quantum error correction near the coding theoretical bound").

- Physical Review Letters (Cao et al.: "Exact Decoding of Quantum Error‑Correcting Codes").

- Institute of Science Tokyo press materials summarising the Komoto & Kasai work.

- IBM research disclosures and reporting on FPGA implementations of quantum decoders.

Comments

No comments yet. Be the first!