新たな符号が量子コンピュータのスケーリングを妨げるノイズを削減

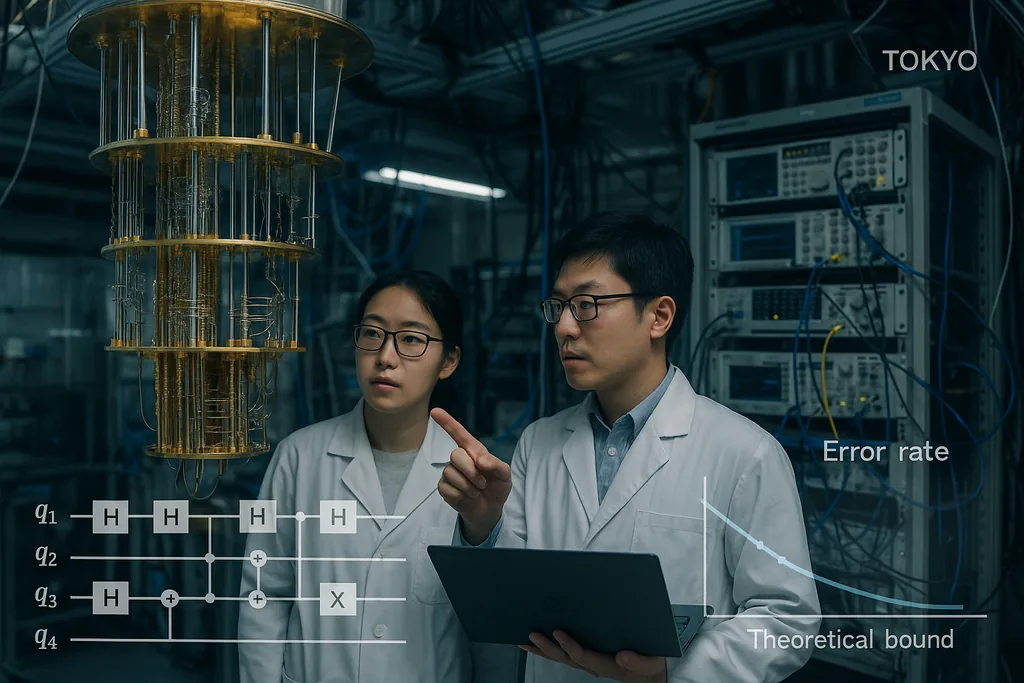

2025年9月30日、東京の研究チームは、効率的に復号可能でありながら、信頼性の高い量子通信と量子計算の長年の理論的限界である「ハッシング限界」に異例なほど近い量子誤り訂正符号を示す論文を発表した。この結果は現在、各機関のレポートで注目されており、単なる一段の魔法のような解決策ではない。それは、低密度パリティ検査(LDPC)構造とその復号器(デコーダ)を注意深く再設計したものであり、それらが一体となってフレーム誤り率を実用的なレベルまで押し下げ、計算オーバーヘッドを低く抑えるものである。容量限界に近い性能と、マシンに応じて線形にスケールする復号コストというこれら2つの特徴こそが、量子プロセッサを実験室の珍品から、化学、暗号学、気候科学における真の課題に取り組めるマシンへと移行させるために必要な特性である。

ノイズのある量子通信路のための容量限界に近い符号

ハッシング限界とは情報理論的な天井であり、最適な符号化と復号を用いた場合に、ノイズのある通信路を通じて量子情報を確実に伝送できる最高速度を示す。歴史的に、効率的であることが証明可能な量子符号は、その限界から遠いか、あるいは実用的でないほど重い復号器を必要としてきた。限界に迫り、かつ控えめにスケールする古典的リソースで復号できる符号を実証することで、KomotoとKasaiは、ハードウェアのスケーリング(数百万の物理量子ビットを配線して多くの論理量子ビットを生み出すプロジェクト)が、理論上の夢物語ではなく現実的な工学的目標であることを説得力を持って示している。

復号器:解決されつつある語られざるボトルネック

誤り訂正符号は物語の半分に過ぎない。高速で正確な復号器がもう半分である。過去1年間で、いくつかのアルゴリズムの進歩が復号のボトルネックを削り取ってきた。2025年6月、研究者たちは特定の符号トポロジーに対する厳密な復号アルゴリズムであるPLANARを説明した。これは、一見手に負えない最尤復号問題を、平面グラフ上の効率的に解けるスピングラス分配関数の計算へと変換するものである。実験データに適用された際、PLANARは論理誤り率を大幅に低減し、ハードウェアの限界に見えていたものの一部が、実は最適ではない復号器によるものであったことを示した。この知見は重要である。なぜなら、より優れた復号器があれば、量子ハードウェアに変更を加えることなく、既存のデバイスからより多くの性能を引き出せることを意味するからだ。

工学的な側面では、業界のチームがこれらの復号のアイデアをリアルタイムの古典的ハードウェアへと移行させている。IBMは最近、主要な誤り訂正アルゴリズムを従来のAMD FPGA上で、超伝導システムにおけるリアルタイム・フィードバックに十分な速さで実行できることを報告し、多くのアーキテクチャで必要とされる速度を大幅に上回る動作を実証した。入手しやすい古典的チップで復号器を動かすことは決定的な一歩である。これにより、誤り訂正はオフラインのコストのかかるソフトウェアプロセスから、大型マシンの制御スタックに組み込み可能な、実用的で低レイテンシのサービスへと変貌する。容量限界に近い符号と相まって、高速なハードウェア復号器は理論と配備可能なシステムの間のループを閉じるものである。

この収束が実際のアプリケーションに意味すること

創薬のための分子シミュレーション、物流の最適化、あるいは新しい暗号プリミティブなど、変革的な価値を約束する量子アプリケーションには、通常、数百万の論理量子ビット、あるいは長時間の計算にわたって維持される極めて低い論理誤り率が必要となる。これまで、誤り訂正の閾値が低く、復号器のコストも高かったため、それらのリソース見積もりは天文学的な数の物理量子ビットへと換算されていた。KomotoとKasaiの符号構成、PLANARのような改良された復号器、そして標準的な古典ハードウェアで復号を実行する推進力の組み合わせは、原理的にそのオーバーヘッドを大幅に削減する。これによりバランスが変化する。以前は実用的でないと判断されていた世代の量子ハードウェアも、工学チームが期待される物理忠実度を備えた中規模の量子ビットアレイを実現できれば、今や手の届くところにあるかもしれない。

この成果に基づいたアプリケーション指向の流れはすでに生まれている。例えば、量子機械学習を研究しているグループは、部分的または近似的な誤り訂正によって、近未来の量子モデルを以前よりもはるかに実用的にし、優位性を示すために必要なハードウェア要求を軽減できることを示した。符号理論、近似的な誤り耐性、そしてアルゴリズム設計のこのような相乗効果は、完全な誤り耐性が実現する前であっても、中間的なマシンでの実用化を加速させる可能性がある。

残された障壁

進歩はあるものの、いくつかの困難な工学的および物理的問題が残っている。Komoto–Kasaiの論文における符号と復号器は、シミュレーションと数値研究で実証されたものである。それらをシリコン、超伝導回路、トラップイオン、あるいはフォトニクスのセットアップに移行するには、極めて厳格なリアルタイム保証を備えた復号パイプラインの構築、極低温スタックを通じた数百万の信号のルーティング、そして宇宙線に起因する相関誤りのような稀だが壊滅的な影響の抑制が必要となる。ハードウェアでの非バイナリ有限体演算の実装、ノイズを加えずにシンドローム抽出を統合すること、そして現実的なデバイスノイズモデルで性能を検証することは、数値的な有望性が運用上の現実になるかどうかを左右する重要な課題である。

また、競合するハードウェア戦略も存在している。一部のグループはハードウェア固有の誤り耐性を向上させている。例えば、フォトニックやキャット量子ビットのアプローチは、自然なノイズバイアスとリソース数の間で異なるトレードオフを主張しており、スケーラブルな復号器が利用可能になるにつれて、これらのアーキテクチャ間のベンチマークが不可欠になるだろう。すべてのアーキテクチャがすべての符号や復号器を等しく活用できるわけではないため、コミュニティには依然としてクロスプラットフォームの検証が必要である。

理論から工学へ:次のステップ

今後の道筋は、調整された3つのトラックによるプログラムのようになるだろう。第一に、符号設計者は、より現実的なノイズモデルや相関誤りを処理し、誤りフロアをさらに下げるために構成を洗練させる。第二に、復号器チームはレイテンシとエネルギーコストを削減し続け、必要に応じてアルゴリズムをFPGA、ASIC、極低温ロジックへと移植する。第三に、ハードウェアグループは実際のデバイスで符号と復号器をベンチマークし、論理誤り率だけでなく、古典計算、配線、冷却、メンテナンスといった隠れたインフラコストについても報告する。これら3つのトラックが収束すれば、コミュニティは量子優位性の抽象的な約束を、有用な仕事をするマシンのための具体的なロードマップへと変えることができるだろう。

要するに、ハッシング限界に近いLDPC符号に関する最近の研究は、孤立した勝利ではなく、よりスマートな符号、より優れた復号器、そして実用的な古典ハードウェアの統合の組み合わせが、理論とアプリケーションの間のギャップを埋めることができるという最新の、そして説得力のある兆候である。広く有用な量子コンピューティングのタイムラインは依然として不透明だが、これらの進歩は、産業や科学のために実用的な仕事をしようとする次世代マシンの構築に向けた工学的な根拠を実質的に改善するものである。

Sources

- npj Quantum Information (Komoto & Kasai: "Quantum error correction near the coding theoretical bound").

- Physical Review Letters (Cao et al.: "Exact Decoding of Quantum Error‑Correcting Codes").

- Institute of Science Tokyo press materials summarising the Komoto & Kasai work.

- IBM research disclosures and reporting on FPGA implementations of quantum decoders.

Comments

No comments yet. Be the first!