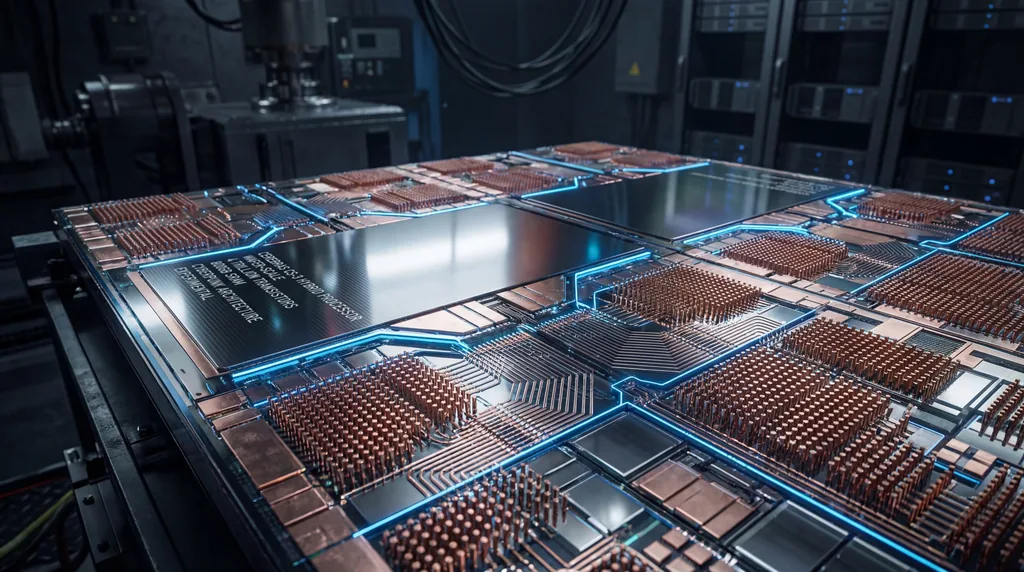

ウエハースケールAIの統合は、数十万のプロセッサコアと大規模な分散メモリを単一の連続したシリコン表面に集約することで、LLMにおけるデータ移動のボトルネックを解消します。 このアーキテクチャの転換は、従来のマルチGPUクラスターに見られる「帯域幅の壁(bandwidth wall)」を取り払うものです。従来のクラスターでは、データがチップの境界を越える際に通信速度が大幅に低下していました。ウエハー・オン・ウエハー(WoW)ハイブリッドボンディングを活用することで、研究者たちは超高帯域幅のインターコネクトを実現しました。これにより、システム全体でシームレスなデータフローが可能になり、現代の大規模言語モデル(LLM)に求められる大規模な並列処理が促進されます。

現代のAIにおけるデータ移動のボトルネック

大規模言語モデルをスケーリングする際の主なボトルネックは、生の演算スループットから、個々のチップ間におけるデータ移動の物理的限界へと移行しています。 NVIDIA DGXシステムを使用するものなど、従来のハイパフォーマンス・コンピューティング(HPC)クラスターでは、個々のGPUは隣接するプロセッサと通信するために必要な物理的なピンや配線によって制限されています。これにより「通信の壁」が生じ、チップ間でデータを移動させるためのエネルギーコストとレイテンシが、学習時間や推論効率を左右する支配的な要因となっています。

インターコネクトのレイテンシは、Transformerベースのモデル学習における同期フェーズで大きなオーバーヘッドを生じさせます。 モデルが数兆個のパラメータに拡大するにつれ、頻繁な「all-reduce」操作(すべての処理ノード間で勾配を共有する操作)の必要性が、従来のネットワークハードウェアに負荷をかけています。これは「ポストGPU」時代の研究につながっており、計算機科学者たちは、次世代の生成AIに必要な高速データフローを維持するために、シリコンウエハー全体を単一の統合されたスーパーチップとして扱う方法を模索しています。

Cerebrasのウエハースケールエンジンとは何か、そしてどのように機能するのか?

Cerebrasのウエハースケールエンジン(WSE)は、数十万のAI最適化コアと数ギガバイトのオンチップSRAMを単一のシリコン片に統合した巨大なシステム・オン・ウエハーです。 ウエハーを小さな個別のチップに切り分ける従来のプロセスを回避することで、WSEはシリコン製造プロセス固有の高帯域幅配線を、215mm x 215mmの表面全体にわたって維持しています。この設計により、大規模なLLM推論のようなメモリバウンドな操作を実行するために不可欠な、超低レイテンシ通信をサポートするメッシュ・アーキテクチャが可能になります。

WSEは、MeshGEMMやMeshGEMVといった特殊な並列化戦略を活用して、分散メモリへのアクセスを最適化することで機能します。 標準的なGPUでは、高帯域幅メモリ(HBM)はプロセッサの外側に配置されており、それがボトルネックとなります。しかし、ウエハースケールのアプローチでは、メモリを演算コアのすぐ隣に配置します。このアーキテクチャにより、外部コンポーネントからデータを取得するという消費電力の大きい低速なプロセスを経ることなく、モデルのプリフィリングやトークン生成に必要な大規模なデータ移動を管理でき、結果としてAIワークロードにおいて数桁速いパフォーマンスを実現します。

ウエハースケール統合とハイブリッドボンディングの解説

ウエハー・オン・ウエハー(WoW)ハイブリッドボンディングは、2つのシリコンウエハーを垂直に積層して高密度の3Dインターコネクトを作成する最先端の製造技術です。 マイクロバンプやハンダを使用してチップを接続する従来のパッケージング手法とは異なり、ハイブリッドボンディングは2つのウエハーの銅パッドを直接融合させます。これにより、平方ミリメートルあたりの接続点数が大幅に増加し、処理要素(PE)間の利用可能な通信領域が実質的に2倍または3倍になり、ウエハースケールAIシステムにおいてより複雑なネットワークトポロジが可能になります。

- インターコネクト密度の向上: ハイブリッドボンディングにより、ウエハー表面全体で数百万もの垂直接続が可能になります。

- 寄生容量の低減: 銅対銅の直接インターフェースにより、電気抵抗とビット転送に必要なエネルギーが低下します。

- 熱管理の強化: ウエハーを積層することで、高度な液冷システムと組み合わせた際の放熱経路を改善できます。

- レチクル統合: このプロセスにより、ウエハーを構成する矩形の「レチクル」(チップ製造の基本単位)間のシームレスな通信が可能になります。

物理的なレチクル配置はウエハースケールチップのネットワークトポロジにどう影響するか?

物理的なレチクル配置は、高速なオンチップ配線がレチクル間またはウエハー間のリンクに移行しなければならない境界を定義することで、実現可能なネットワークトポロジを決定します。 標準的なウエハースケールAIの設計では、リソグラフィプロセスによって単一の機能ユニット(レチクル)のサイズが制限されるため、ウエハー全体をカバーするにはステッピングパターンが必要になります。Luca Benini氏、Torsten Hoefler氏、Maciej Besta氏らを含む研究チームは、これらのレチクルを整列させる方法(完全に重ねるか、ずらすか)がデータの通る経路を決定し、レイテンシとスループットに直接影響を与えることを発見しました。

洗練された配置戦略により、離れた処理コア間の「ホップ数」を大幅に削減できます。 研究チームは、Aligned(整列)、Interleaved(インターリーブ)、Rotated(回転)、Contoured(輪郭)という4つの主要な構成を調査しました。ハイブリッドボンディングのプロセス中にレチクルを戦略的にずらしたり回転させたりすることで、標準的な2Dメッシュでは不可能なショートカットパスを作成することに成功しました。例えば、「Contoured」配置では、ネットワークがウエハーの自然な円形形状に従うことができ、エッジケースのシリコンの利用を最適化し、ディープラーニング・タスクのためのより効率的なグローバル通信ファブリックを構築できます。

トポロジの最適化:4つのレチクル配置戦略

ウエハースケールネットワークのベースラインは通常2Dメッシュですが、これは硬直的な格子状の接続性によって制限されています。 2Dメッシュは機能的ではあるものの、データがウエハーの一端から他端まで移動しなければならない場合に高いレイテンシが生じます。これに対処するため、Hoefler氏らが発表した研究では、ウエハーの物理的な配置を操作してデータの「特急レーン」を作成できることが示唆されています。Aligned戦略とInterleaved戦略は、結合された2つのウエハー間の垂直接続を簡素化し、すべての処理コアが反対側のレイヤーに直接のパートナーを持つようにすることに焦点を当てています。

Rotated(回転)やContoured(輪郭)といった高度な構成は、ハイパフォーマンスなネットワーク設計におけるブレークスルーを象徴しています。 Rotated戦略では、ボンディング前に一方のウエハーを90度回転させることで、物理レイアウトをハイラディックス(高次数)ネットワークに変換します。この構成により、余分な物理配線を追加することなく、ウエハーを横断する「長距離」ホップが可能になります。これらの最適化されたトポロジにより、スパースなAIモデルで頻繁に見られる不規則なデータパターンをネットワークが処理できるようになり、さまざまなニューラルネットワーク・アーキテクチャに適応可能な柔軟なインフラストラクチャが提供されます。

利益の定量化:パフォーマンスと効率

最適化されたレチクル配置戦略の実装により、従来の2Dメッシュのベースラインと比較して、ネットワークスループットが250%という大幅な向上を記録しました。 このパフォーマンスの飛躍は、主にネットワーク混雑の緩和によるものです。データにより直接的な経路を提供することで、システムはより大量の情報を同時に移動させることができます。大規模言語モデルにとって、これは学習をしばしば停滞させる「all-reduce」や「all-to-all」の通信パターンを、わずかな時間で完了できることを意味します。

生の速度だけでなく、この研究はレイテンシとエネルギーの持続可能性における顕著な改善も強調しています。

- レイテンシの削減: 通信遅延が最大36%短縮され、モデルの重みのより高速な同期が可能になりました。

- エネルギー効率: 転送バイトあたりに必要なエネルギーが最大38%減少し、これはAIの環境負荷における重要な指標となります。

- システムの信頼性: ホップ数とデータが移動する電気的な距離を減らすことで、研究者たちは通信ファブリック全体の堅牢性も向上させました。

業界への影響:Cerebrasから未来のスーパーチップへ

この研究は、個々のGPUチップの限界を超え、半導体製造の未来に向けたロードマップを提示しています。 Cerebras Systemsのような企業がすでにウエハースケールエンジンの実現可能性を証明していますが、チューリッヒ工科大学(ETH Zurich)のTorsten Hoefler氏らのチームによる成果は、私たちがまだ可能性の入り口に立ったばかりであることを示唆しています。ウエハー・オン・ウエハー・ボンディングと高度なトポロジ設計を活用することで、将来のスーパーチップは単一のパッケージに数兆個のトランジスタを搭載し、GPT-4を遥かに凌ぐ規模のモデルを学習させるために必要なハードウェアを提供できる可能性があります。

統合されたウエハースケールAIへの移行は、AIハードウェア市場の競争を再定義することになるでしょう。 LLMへの需要が急増し続ける中、スループットを最大化しながらエネルギー消費を最小限に抑える能力が、主要な競争優位性となります。「チップのクラスター」を構築することから「ウエハースケールシステム」へと移行することは、コンピュータアーキテクチャの考え方における根本的な変化を意味しており、ハードウェアの物理的なサイズだけがモデルの知能を制限する唯一の要因となる未来を約束しています。

Comments

No comments yet. Be the first!