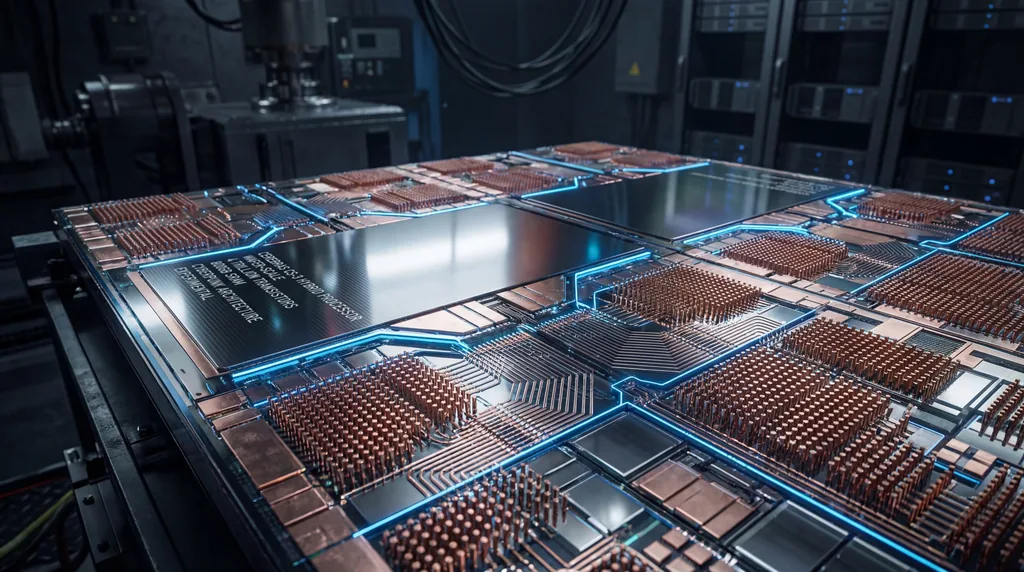

Интеграция ИИ на уровне пластины (Wafer-Scale AI) решает проблему «бутылочного горлышка» при передаче данных в больших языковых моделях (LLM) путем объединения сотен тысяч процессорных ядер и огромных объемов распределенной памяти на единой непрерывной поверхности кремния. Этот архитектурный сдвиг устраняет «барьер пропускной способности», характерный для традиционных мульти-GPU кластеров, где скорость передачи данных значительно падает при пересечении границ чипа. Используя гибридное сращивание пластин (wafer-on-wafer, WoW), исследователи создали межсоединения со сверхвысокой пропускной способностью, которые обеспечивают беспрепятственный поток данных по всей системе, упрощая массивно-параллельную обработку, необходимую для современных больших языковых моделей (LLM).

Проблема передачи данных в современном ИИ

Основное препятствие для масштабирования больших языковых моделей сместилось с чистой вычислительной мощности на физические ограничения передачи данных между отдельными чипами. В обычных высокопроизводительных вычислительных кластерах, таких как системы NVIDIA DGX, отдельные графические процессоры ограничены физическими контактами и разводкой, необходимыми для связи с соседними процессорами. Это создает «коммуникационную стену», где энергетические затраты и задержка при перемещении данных между чипами становятся доминирующими факторами, влияющими на время обучения и эффективность вывода (инференса).

Задержка межсоединений создает значительные накладные расходы на этапах синхронизации при обучении моделей на базе архитектуры Transformer. По мере того как модели разрастаются до триллионов параметров, потребность в частых операциях «all-reduce» — когда градиенты распределяются между всеми узлами обработки — перегружает традиционное сетевое оборудование. Это привело к началу исследовательской эры «Post-GPU», в которой специалисты по компьютерным наукам ищут способы рассматривать всю кремниевую пластину как единый унифицированный суперчип для поддержания высокоскоростного потока данных, необходимого для следующего поколения генеративного ИИ.

Что такое wafer-scale engine от Cerebras и как он работает?

Wafer-scale engine (WSE) компании Cerebras — это массивная система на пластине, объединяющая сотни тысяч оптимизированных для ИИ ядер и гигабайты встроенной памяти SRAM на одном куске кремния. Обходя традиционный процесс разрезания пластин на мелкие отдельные чипы, WSE сохраняет высокоскоростную разводку, присущую процессу производства кремния, на всей поверхности размером 215 мм x 215 мм. Такая конструкция позволяет реализовать сетчатую архитектуру (mesh architecture), которая поддерживает связь с ультранизкой задержкой, что критически важно для выполнения операций с интенсивным использованием памяти, таких как инференс больших языковых моделей в промышленных масштабах.

WSE функционирует за счет использования специализированных стратегий параллелизма, таких как MeshGEMM и MeshGEMV, для оптимизации доступа к распределенной памяти. В стандартном GPU память с высокой пропускной способностью (HBM) расположена вне процессора, что создает узкое место; однако подход на уровне пластины размещает память непосредственно рядом с вычислительными ядрами. Эта архитектура позволяет системе управлять масштабным перемещением данных, необходимым для префиллинга (prefilling) моделей и генерации токенов, без энергозатратного и медленного процесса извлечения данных из внешних компонентов, что приводит к многократному увеличению производительности ИИ-нагрузок.

Объяснение интеграции на уровне пластины и гибридного сращивания

Гибридное сращивание пластин (WoW) — это передовая технология производства, при которой две кремниевые пластины накладываются друг на друга вертикально для создания 3D-межсоединений высокой плотности. В отличие от традиционных методов упаковки, в которых для соединения чипов используются микроконтакты или припой, гибридное сращивание напрямую сплавляет медные контактные площадки двух пластин. Это обеспечивает значительно большее количество точек соединения на квадратный миллиметр, фактически удваивая или утраивая доступную область связи между процессорными элементами (PE) и позволяя создавать гораздо более сложные топологии сетей в системах Wafer-Scale AI.

- Повышенная плотность межсоединений: Гибридное сращивание позволяет создавать миллионы вертикальных соединений по всей поверхности пластины.

- Снижение паразитной емкости: Прямой интерфейс «медь-медь» снижает электрическое сопротивление и энергию, необходимую для передачи битов.

- Улучшенное управление тепловыделением: Стекирование пластин может улучшить пути рассеивания тепла в сочетании с передовым жидкостным охлаждением.

- Интеграция ретикул: Процесс обеспечивает бесперебойную связь между прямоугольными «ретикулами» (базовыми единицами производства чипов), из которых состоит пластина.

Как физическое размещение ретикул влияет на топологию сети в чипах масштаба пластины?

Физическое размещение ретикул диктует достижимую топологию сети, определяя границы, где высокоскоростная внутрикристальная разводка должна переходить в межретикульные или межпластинные соединения. В стандартном дизайне Wafer-Scale AI процесс литографии ограничивает размер одного функционального блока (ретикулы), что требует повторяющегося паттерна для покрытия всей пластины. Исследователи, в том числе Luca Benini, Torsten Hoefler и Maciej Besta, обнаружили, что способ выравнивания этих ретикул — будь то идеальное совмещение или смещение — определяет путь, по которому должны проходить данные, напрямую влияя на задержку и пропускную способность.

Сложные стратегии размещения могут значительно сократить «количество скачков» (hop count) между удаленными процессорными ядрами. Исследовательская группа изучила четыре основные конфигурации: Выровненная (Aligned), Чередующаяся (Interleaved), Повернутая (Rotated) и Контурная (Contoured). Стратегически смещая или поворачивая ретикулы в процессе гибридного сращивания, они смогли создать пути-сокращения, которые были бы невозможны в стандартной 2D-сетке. Например, «контурное» размещение позволяет сети следовать естественной круглой форме пластины, оптимизируя использование кремния по краям и создавая более эффективную глобальную коммуникационную среду для задач глубокого обучения.

Оптимизация топологии: четыре стратегии размещения ретикул

Базовым вариантом для сетей масштаба пластины обычно является 2D-сетка, которая ограничена своей жесткой решетчатой связностью. Несмотря на функциональность, 2D-сетка страдает от высокой задержки, когда данным приходится перемещаться с одной стороны пластины на другую. Чтобы решить эту проблему, исследование, представленное Hoefler и его коллегами, предполагает, что физическим расположением пластин можно манипулировать для создания «экспресс-полос» для данных. Стратегии Aligned и Interleaved направлены на упрощение вертикальных соединений между двумя скрепленными пластинами, чтобы каждое процессорное ядро имело прямого партнера на противоположном слое.

Продвинутые конфигурации, такие как Rotated и Contoured, представляют собой прорыв в проектировании высокопроизводительных сетей. Стратегия Rotated подразумевает поворот одной пластины на 90 градусов перед сращиванием, что превращает физическую компоновку в сеть с высокой степенью (high-radix). Эта конфигурация позволяет совершать «дальние» скачки по пластине без добавления лишней физической разводки. Такие оптимизированные топологии гарантируют, что сеть сможет справляться с нерегулярными паттернами данных, часто встречающимися в разреженных моделях ИИ, обеспечивая гибкую инфраструктуру, способную адаптироваться к различным архитектурам нейронных сетей.

Количественная оценка результатов: производительность и эффективность

Внедрение оптимизированных стратегий размещения ретикул привело к колоссальному увеличению пропускной способности сети на 250% по сравнению с традиционными базовыми 2D-сетками. Этот скачок производительности в первую очередь обусловлен уменьшением перегрузки сети: предоставляя более прямые пути для данных, система может перемещать большие объемы информации одновременно. Для больших языковых моделей это означает, что паттерны обмена данными «all-reduce» и «all-to-all», которые часто тормозят обучение, могут быть выполнены за долю прежнего времени.

Помимо чистой скорости, исследование подчеркивает значительные улучшения в задержке и энергетической устойчивости.

- Сокращение задержки: Задержки связи были сокращены на величину до 36%, что обеспечивает более быструю синхронизацию весов модели.

- Энергоэффективность: Энергия, необходимая для передачи одного байта, снизилась на величину до 38%, что является критически важным показателем для снижения воздействия ИИ на окружающую среду.

- Надежность системы: Уменьшив количество скачков и электрическое расстояние, которое должны проходить данные, исследователи также повысили общую отказоустойчивость коммуникационной среды.

Последствия для отрасли: от Cerebras к суперчипам будущего

Это исследование дает дорожную карту для будущего производства полупроводников, выходящего за пределы возможностей отдельных чипов GPU. Хотя такие компании, как Cerebras Systems, уже доказали жизнеспособность процессоров масштаба пластины, работа Torsten Hoefler и его команды в ETH Zurich показывает, что мы находимся только в начале пути. Используя сращивание пластин и передовой дизайн топологии, будущие суперчипы смогут вмещать триллионы транзисторов в одном корпусе, обеспечивая аппаратную базу, необходимую для обучения моделей, намного превосходящих GPT-4.

Переход к интегрированному Wafer-Scale AI, вероятно, изменит расстановку сил на рынке оборудования для ИИ. Поскольку спрос на LLM продолжает стремительно расти, способность минимизировать энергопотребление при максимизации пропускной способности станет основным конкурентным преимуществом. Переход от создания «кластеров чипов» к «системам масштаба пластины» представляет собой фундаментальное изменение в нашем представлении о компьютерной архитектуре, обещающее будущее, в котором физический размер нашего оборудования будет единственным ограничением для интеллекта наших моделей.

Comments

No comments yet. Be the first!