Die Integration von Wafer-Scale-KI adressiert Engpässe beim Datentransport in LLMs, indem sie Hunderttausende von Prozessorkernen und massiven verteilten Speicher auf einer einzigen, kontinuierlichen Siliziumoberfläche konsolidiert. Dieser architektonische Wandel eliminiert die „Bandbreitenwand“ (Bandwidth Wall) herkömmlicher Multi-GPU-Cluster, bei denen die Kommunikationsgeschwindigkeiten erheblich sinken, sobald Daten Chipgrenzen überschreiten. Durch den Einsatz von Wafer-on-Wafer (WoW) Hybrid-Bonding haben Forscher extrem hochbandbreitige Interconnects ermöglicht, die einen nahtlosen Datenfluss über das gesamte System hinweg erlauben und die für moderne große Sprachmodelle (LLMs) erforderliche massive parallele Verarbeitung erleichtern.

Der Datentransport-Engpass in der modernen KI

Der primäre Engpass für die Skalierung großer Sprachmodelle hat sich vom reinen Rechendurchsatz hin zu den physischen Grenzen des Datentransports zwischen einzelnen Chips verlagert. In herkömmlichen Hochleistungsrechner-Clustern, wie sie beispielsweise in NVIDIA DGX-Systemen verwendet werden, sind einzelne GPUs durch die physischen Pins und die Verkabelung begrenzt, die für die Kommunikation mit benachbarten Prozessoren erforderlich sind. Dies schafft eine „Kommunikationswand“, bei der die Energiekosten und die Latenz beim Verschieben von Daten zwischen den Chips zu den dominierenden Faktoren für Trainingszeit und Inferenz-Effizienz werden.

Die Interconnect-Latenz verursacht erheblichen Overhead während der Synchronisationsphasen beim Training von Transformer-basierten Modellen. Da Modelle auf Billionen von Parametern anwachsen, belastet die Notwendigkeit häufiger „All-Reduce“-Operationen – bei denen Gradienten über alle Verarbeitungsknoten hinweg geteilt werden – die herkömmliche Netzwerk-Hardware. Dies hat zu einer „Post-GPU“-Ära in der Forschung geführt, in der Computerwissenschaftler nach Wegen suchen, einen gesamten Silizium-Wafer als einen einzigen, einheitlichen Super-Chip zu behandeln, um den für die nächste Generation generativer KI notwendigen Hochgeschwindigkeits-Datenfluss aufrechtzuerhalten.

Was ist die Wafer-Scale Engine von Cerebras und wie funktioniert sie?

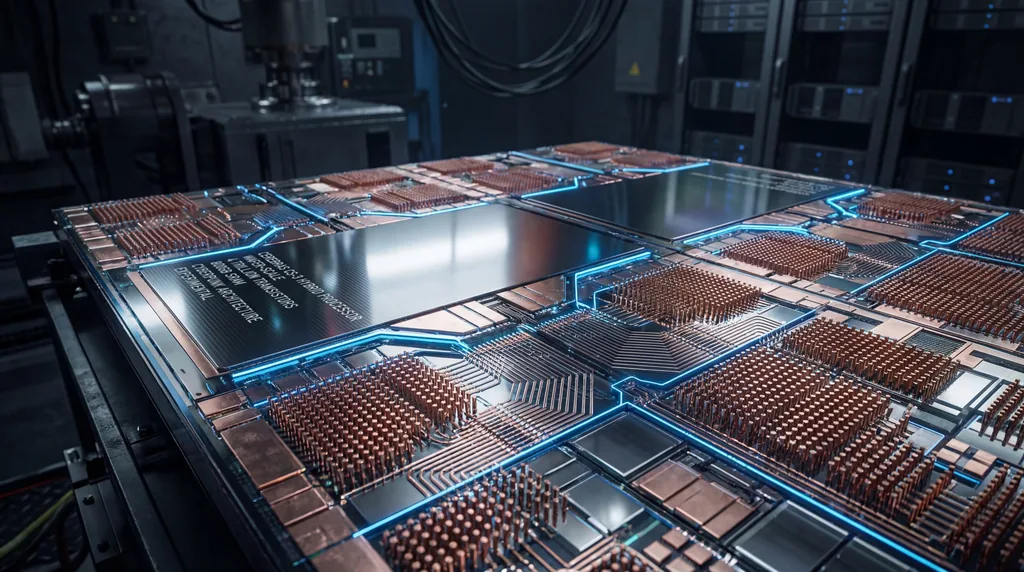

Die Wafer-Scale Engine (WSE) von Cerebras ist ein massives System-on-Wafer, das Hunderttausende von KI-optimierten Kernen und Gigabytes an On-Chip-SRAM auf einem einzigen Stück Silizium integriert. Indem der traditionelle Prozess des Zerschneidens von Wafern in kleine Einzelchips umgangen wird, behält die WSE die dem Silizium-Herstellungsprozess inhärente hochbandbreitige Verkabelung über die gesamte 215 mm x 215 mm große Oberfläche bei. Dieses Design ermöglicht eine Mesh-Architektur, die eine Kommunikation mit extrem niedriger Latenz unterstützt, was für die Ausführung speichergebundener Operationen wie der Inferenz von großen Sprachmodellen in großem Maßstab entscheidend ist.

Die WSE funktioniert durch den Einsatz spezialisierter Parallelisierungsstrategien wie MeshGEMM und MeshGEMV, um den Zugriff auf den verteilten Speicher zu optimieren. In einer Standard-GPU befindet sich der High-Bandwidth Memory (HBM) außerhalb des Prozessors, was einen Engpass erzeugt; der Wafer-Scale-Ansatz platziert den Speicher jedoch direkt neben den Rechenkernen. Diese Architektur erlaubt es dem System, die massiven Datenbewegungen zu bewältigen, die für das Prefilling von Modellen und die Token-Generierung erforderlich sind, ohne den stromfressenden und langsamen Prozess des Datenabrufs von externen Komponenten, was zu einer um Größenordnungen schnelleren Leistung für KI-Workloads führt.

Wafer-Scale-Integration und Hybrid-Bonding erklärt

Wafer-on-Wafer (WoW) Hybrid-Bonding ist eine hochmoderne Fertigungstechnik, bei der zwei Silizium-Wafer vertikal gestapelt werden, um einen hochdichten 3D-Interconnect zu schaffen. Im Gegensatz zu herkömmlichen Packaging-Methoden, die Micro-Bumps oder Lötmittel zur Verbindung von Chips verwenden, verschmilzt Hybrid-Bonding die Kupfer-Pads zweier Wafer direkt miteinander. Dies ermöglicht eine deutlich höhere Anzahl von Verbindungspunkten pro Quadratmillimeter, was die verfügbare Kommunikationsfläche zwischen den Verarbeitungselementen (PEs) effektiv verdoppelt oder verdreifacht und viel komplexere Netzwerktopologien in Wafer-Scale-KI-Systemen erlaubt.

- Erhöhte Interconnect-Dichte: Hybrid-Bonding ermöglicht Millionen von vertikalen Verbindungen über die Waferoberfläche hinweg.

- Reduzierte parasitäre Kapazität: Die direkte Kupfer-zu-Kupfer-Schnittstelle senkt den elektrischen Widerstand und die für die Übertragung von Bits benötigte Energie.

- Verbessertes thermisches Management: Das Stapeln von Wafern kann in Kombination mit fortschrittlicher Flüssigkeitskühlung die Wärmeableitungspfade verbessern.

- Retikel-Integration: Der Prozess ermöglicht eine nahtlose Kommunikation zwischen den rechteckigen „Retikeln“ (den Grundeinheiten der Chipherstellung), aus denen der Wafer besteht.

Wie beeinflusst die physische Platzierung der Retikel die Netzwerktopologie in Wafer-Scale-Chips?

Die physische Platzierung der Retikel diktiert die erreichbare Netzwerktopologie, indem sie die Grenzen definiert, an denen hochgeschwindigkeits On-Chip-Verkabelungen in Inter-Retikel- oder Inter-Wafer-Verbindungen übergehen müssen. In einem Standard-Wafer-Scale-KI-Design begrenzt der Lithografieprozess die Größe einer einzelnen Funktionseinheit (das Retikel), was ein Stepping-Muster erfordert, um den gesamten Wafer abzudecken. Die Forscher, darunter Luca Benini, Torsten Hoefler und Maciej Besta, fanden heraus, dass die Art und Weise, wie diese Retikel ausgerichtet sind – ob sie perfekt gestapelt oder verschoben sind – den Pfad bestimmt, den die Daten nehmen müssen, was sich direkt auf Latenz und Durchsatz auswirkt.

Ausgeklügelte Platzierungsstrategien können die Anzahl der Hops („Hop Count“) zwischen weit entfernten Rechenkernen erheblich reduzieren. Das Forschungsteam untersuchte vier primäre Konfigurationen: Aligned (ausgerichtet), Interleaved (verschachtelt), Rotated (rotiert) und Contoured (konturiert). Durch strategisches Verschieben oder Rotieren der Retikel während des Hybrid-Bonding-Prozesses konnten sie Abkürzungspfade schaffen, die in einem Standard-2D-Mesh unmöglich wären. Beispielsweise ermöglicht eine „Contoured“-Platzierung dem Netzwerk, der natürlichen Kreisform des Wafers zu folgen, wodurch die Nutzung von Rand-Silizium optimiert und eine effizientere globale Kommunikationsstruktur für Deep-Learning-Aufgaben geschaffen wird.

Topologie-Optimierung: Die vier Retikel-Platzierungsstrategien

Die Basis für Wafer-Scale-Netzwerke ist in der Regel ein 2D-Mesh, das durch seine starre, gitterartige Konnektivität begrenzt ist. Obwohl funktional, leidet das 2D-Mesh unter hohen Latenzzeiten, wenn Daten von einer Seite des Wafers zur anderen reisen müssen. Um dies zu adressieren, legt die von Hoefler und seinen Kollegen vorgestellte Forschung nahe, dass die physische Anordnung der Wafer manipuliert werden kann, um „Expressspuren“ für Daten zu schaffen. Die Strategien Aligned und Interleaved konzentrieren sich auf die Vereinfachung der vertikalen Verbindungen zwischen zwei gebondeten Wafern, um sicherzustellen, dass jeder Rechenkern einen direkten Partner auf der gegenüberliegenden Schicht hat.

Fortschrittliche Konfigurationen wie die Rotated- und Contoured-Platzierungen stellen einen Durchbruch im Bereich des Hochleistungs-Netzwerkdesigns dar. Die Rotated-Strategie beinhaltet das Drehen eines Wafers um 90 Grad vor dem Bonden, was das physische Layout in ein High-Radix-Netzwerk transformiert. Diese Konfiguration ermöglicht „Long-Range-Hops“ über den Wafer hinweg, ohne zusätzliche physische Verkabelung hinzuzufügen. Diese optimierten Topologien stellen sicher, dass das Netzwerk die unregelmäßigen Datenmuster bewältigen kann, die oft in Sparse-KI-Modellen auftreten, und bieten eine flexible Infrastruktur, die sich an verschiedene neuronale Netzwerkarchitekturen anpassen kann.

Quantifizierung der Gewinne: Leistung und Effizienz

Die Implementierung optimierter Retikel-Platzierungsstrategien führte zu einer massiven Steigerung des Netzdurchsatzes um 250 % im Vergleich zu herkömmlichen 2D-Mesh-Baselines. Dieser Leistungssprung ist primär auf die Reduzierung von Netzwerkengpässen zurückzuführen; durch die Bereitstellung direkterer Pfade für Daten kann das System gleichzeitig größere Informationsmengen bewegen. Für große Sprachmodelle bedeutet dies, dass die Kommunikationsmuster „All-Reduce“ und „All-to-All“, die das Training oft ins Stocken bringen, in einem Bruchteil der Zeit abgeschlossen werden können.

Über die reine Geschwindigkeit hinaus hebt die Forschung signifikante Verbesserungen bei Latenz und Energienachhaltigkeit hervor.

- Latenzreduzierung: Kommunikationsverzögerungen wurden um bis zu 36 % gesenkt, was eine schnellere Synchronisation der Modellgewichte ermöglicht.

- Energieeffizienz: Die pro übertragenem Byte benötigte Energie sank um bis zu 38 %, eine entscheidende Kennzahl für die Umweltauswirkungen von KI.

- Systemzuverlässigkeit: Durch die Reduzierung der Hop-Anzahl und der elektrischen Distanz, die Daten zurücklegen müssen, verbesserten die Forscher auch die allgemeine Robustheit der Kommunikationsstruktur.

Branchenauswirkungen: Von Cerebras zu zukünftigen Super-Chips

Diese Forschung liefert einen Fahrplan für die Zukunft der Halbleiterfertigung, die über die Grenzen einzelner GPU-Chips hinausgeht. Während Unternehmen wie Cerebras Systems die Machbarkeit von Wafer-Scale-Engines bereits bewiesen haben, deutet die Arbeit von Torsten Hoefler und seinem Team an der ETH Zürich darauf hin, dass wir erst am Anfang dessen stehen, was möglich ist. Durch den Einsatz von Wafer-on-Wafer-Bonding und fortschrittlichem Topologie-Design könnten zukünftige Super-Chips Billionen von Transistoren in einem einzigen Gehäuse beherbergen und so die Hardware bereitstellen, die erforderlich ist, um Modelle zu trainieren, die weit größer sind als GPT-4.

Die Verschiebung hin zu integrierter Wafer-Scale-KI wird wahrscheinlich den Wettbewerb auf dem KI-Hardwaremarkt neu definieren. Da die Nachfrage nach LLMs weiterhin rasant steigt, wird die Fähigkeit, den Energieverbrauch zu minimieren und gleichzeitig den Durchsatz zu maximieren, zum primären Wettbewerbsvorteil. Der Übergang vom Bau von „Chip-Clustern“ zu „Wafer-Scale-Systemen“ stellt einen grundlegenden Wandel in unserem Verständnis von Computerarchitektur dar und verspricht eine Zukunft, in der die physische Größe unserer Hardware die einzige Grenze für die Intelligenz unserer Modelle ist.

Kommentare

Noch keine Kommentare. Seien Sie der Erste!