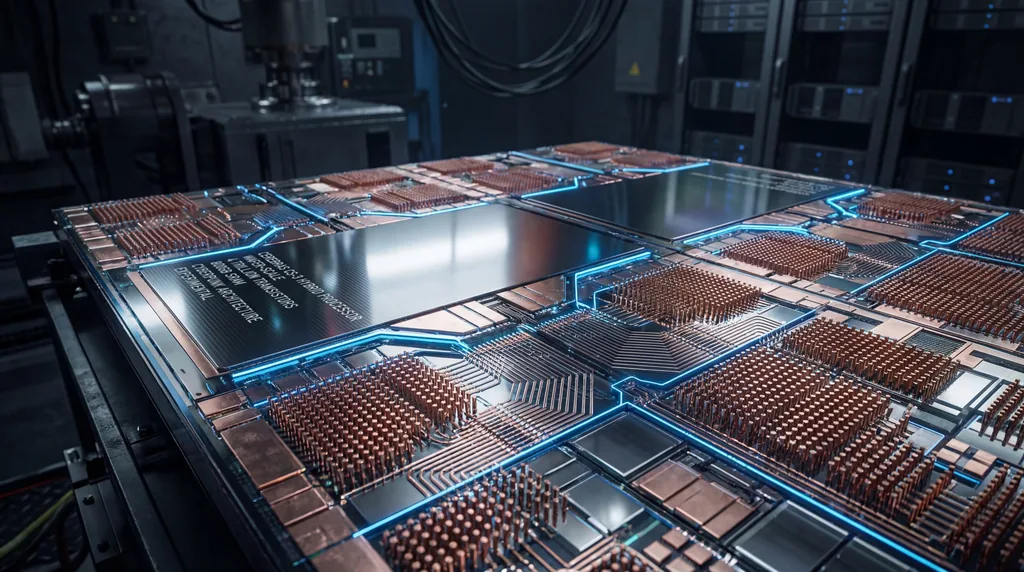

Integracja AI w skali wafla (wafer-scale integration) rozwiązuje problem wąskich gardeł w przesyłaniu danych w modelach LLM poprzez konsolidację setek tysięcy rdzeni procesorów i ogromnej pamięci rozproszonej na pojedynczej, ciągłej powierzchni krzemu. Ta zmiana architektoniczna eliminuje „ścianę przepustowości” występującą w tradycyjnych klastrach wielo-GPU, gdzie prędkość komunikacji znacznie spada, gdy dane przekraczają granice chipa. Wykorzystując hybrydowe wiązanie typu wafer-on-wafer (WoW), naukowcy umożliwili stworzenie interkonektów o ultrawysokiej przepustowości, które pozwalają na płynny przepływ danych w całym systemie, ułatwiając masowe przetwarzanie równoległe wymagane przez nowoczesne wielkie modele językowe (LLM).

Wąskie gardło przesyłania danych we współczesnej sztucznej inteligencji

Główne wąskie gardło przy skalowaniu wielkich modeli językowych przesunęło się z surowej mocy obliczeniowej na fizyczne ograniczenia przesyłania danych między poszczególnymi układami. W konwencjonalnych klastrach obliczeniowych o wysokiej wydajności, takich jak te wykorzystujące systemy NVIDIA DGX, poszczególne procesory GPU są ograniczone przez fizyczne piny i okablowanie wymagane do komunikacji z sąsiednimi procesorami. Tworzy to „ścianę komunikacyjną”, w której koszt energetyczny i opóźnienia przesyłania danych między chipami stają się dominującymi czynnikami wpływającymi na czas trenowania i wydajność wnioskowania.

Opóźnienia interkonektów generują znaczny narzut podczas faz synchronizacji w treningu modeli opartych na architekturze Transformer. W miarę jak modele rozrastają się do bilionów parametrów, potrzeba częstych operacji „all-reduce” – w których gradienty są współdzielone przez wszystkie węzły przetwarzające – obciąża tradycyjny sprzęt sieciowy. Doprowadziło to do ery badań „Post-GPU”, w której informatycy szukają sposobów na traktowanie całego wafla krzemowego jako pojedynczego, ujednoliconego super-chipa, aby utrzymać szybki przepływ danych niezbędny dla następnej generacji generatywnej sztucznej inteligencji.

Czym jest silnik w skali wafla firmy Cerebras i jak działa?

Wafer-Scale Engine (WSE) firmy Cerebras to potężny system typu system-on-wafer, który integruje setki tysięcy rdzeni zoptymalizowanych pod kątem AI oraz gigabajty pamięci SRAM na jednym kawałku krzemu. Omijając tradycyjny proces cięcia wafla na małe, pojedyncze chipy, WSE utrzymuje wysoką przepustowość okablowania nieodłącznie związaną z procesem produkcji krzemu na całej powierzchni 215 mm x 215 mm. Taka konstrukcja pozwala na zastosowanie architektury siatki (mesh), która obsługuje komunikację o ultraniskich opóźnieniach, co ma kluczowe znaczenie dla wykonywania operacji ograniczonych pamięciowo, takich jak wnioskowanie w wielkich modelach językowych na dużą skalę.

WSE funkcjonuje dzięki wykorzystaniu wyspecjalizowanych strategii równoległości, takich jak MeshGEMM i MeshGEMV, w celu optymalizacji dostępu do pamięci rozproszonej. W standardowym procesorze GPU pamięć o wysokiej przepustowości (HBM) znajduje się na zewnątrz procesora, co tworzy wąskie gardło; jednak podejście w skali wafla umieszcza pamięć bezpośrednio przy rdzeniach obliczeniowych. Architektura ta pozwala systemowi zarządzać masowym przesyłem danych wymaganym do prefillingu modeli i generowania tokenów bez energochłonnego i powolnego procesu pobierania danych z zewnętrznych komponentów, co skutkuje o rzędy wielkości szybszą wydajnością w zadaniach AI.

Wyjaśnienie integracji w skali wafla i hybrydowego wiązania

Hybrydowe wiązanie typu wafer-on-wafer (WoW) to przełomowa technika produkcyjna polegająca na pionowym układaniu dwóch waflów krzemowych w celu stworzenia interkonektu 3D o wysokiej gęstości. W przeciwieństwie do tradycyjnych metod pakowania, które wykorzystują mikrowypustki (micro-bumps) lub lut do łączenia chipów, wiązanie hybrydowe bezpośrednio łączy miedziane pola stykowe dwóch waflów. Zapewnia to znacznie większą liczbę punktów połączeń na milimetr kwadratowy, skutecznie podwajając lub potrajając dostępny obszar komunikacji między elementami przetwarzającymi (PE) i pozwalając na znacznie bardziej złożone topologie sieci w systemach Wafer-Scale AI.

- Zwiększona gęstość interkonektów: Wiązanie hybrydowe pozwala na miliony pionowych połączeń na całej powierzchni wafla.

- Zredukowana pojemność pasożytnicza: Bezpośredni interfejs miedź-miedź obniża oporność elektryczną i energię wymaganą do przesyłania bitów.

- Ulepszone zarządzanie termiczne: Układanie waflów warstwowo może poprawić drogi rozpraszania ciepła w połączeniu z zaawansowanym chłodzeniem cieczą.

- Integracja pól reticle: Proces ten umożliwia płynną komunikację między prostokątnymi polami „reticle” (podstawowymi jednostkami produkcji chipów), które tworzą wafel.

Jak fizyczne rozmieszczenie pól reticle wpływa na topologię sieci w układach w skali wafla?

Fizyczne rozmieszczenie pól reticle dyktuje osiągalną topologię sieci, definiując granice, w których szybkie okablowanie wewnątrz układu musi przejść w połączenia między polami reticle lub między waflami. W standardowym projekcie Wafer-Scale AI proces litografii ogranicza rozmiar pojedynczej jednostki funkcjonalnej (reticle), co wymaga powtarzalnego wzoru w celu pokrycia całego wafla. Badacze, w tym Luca Benini, Torsten Hoefler i Maciej Besta, odkryli, że sposób wyrównania tych pól – niezależnie od tego, czy są one idealnie ułożone jedno nad drugim, czy przesunięte – determinuje ścieżkę, którą muszą pokonać dane, bezpośrednio wpływając na opóźnienia i przepustowość.

Zaawansowane strategie rozmieszczania mogą znacznie zmniejszyć liczbę przeskoków (hop count) między odległymi rdzeniami przetwarzającymi. Zespół badawczy zbadał cztery główne konfiguracje: Aligned (wyrównaną), Interleaved (przeplataną), Rotated (obróconą) i Contoured (konturową). Dzięki strategicznemu przesuwaniu lub obracaniu pól reticle podczas procesu hybrydowego wiązania, byli w stanie stworzyć ścieżki na skróty, które byłyby niemożliwe w standardowej sieci 2D mesh. Na przykład rozmieszczenie „Contoured” pozwala sieci podążać za naturalnym kołowym kształtem wafla, optymalizując wykorzystanie krzemu na krawędziach i tworząc bardziej wydajną globalną strukturę komunikacyjną dla zadań uczenia głębokiego.

Optymalizacja topologii: cztery strategie rozmieszczenia pól reticle

Punktem odniesienia dla sieci w skali wafla jest zazwyczaj struktura 2D mesh, którą ogranicza sztywna, siatkowa łączność. Chociaż jest funkcjonalna, sieć 2D mesh cierpi z powodu wysokich opóźnień, gdy dane muszą przemieścić się z jednej strony wafla na drugą. Aby temu zaradzić, badania przedstawione przez Hoeflera i jego współpracowników sugerują, że fizyczny układ waflów można modyfikować w celu stworzenia „szybkich pasów” dla danych. Strategie Aligned i Interleaved koncentrują się na uproszczeniu pionowych połączeń między dwoma połączonymi waflami, aby zapewnić, że każdy rdzeń przetwarzający ma bezpośredniego partnera w przeciwnej warstwie.

Zaawansowane konfiguracje, takie jak rozmieszczenia Rotated i Contoured, stanowią przełom w projektowaniu sieci o wysokiej wydajności. Strategia Rotated polega na obróceniu jednego wafla o 90 stopni przed związaniem, co przekształca fizyczny układ w sieć o wysokim rzędzie (high-radix). Konfiguracja ta pozwala na przeskoki „dalekiego zasięgu” przez wafel bez dodawania dodatkowego fizycznego okablowania. Te zoptymalizowane topologie zapewniają, że sieć może obsługiwać nieregularne wzorce danych często spotykane w rzadkich modelach AI, dostarczając elastyczną infrastrukturę, która może dostosować się do różnych architektur sieci neuronowych.

Ilościowe określenie zysków: wydajność i efektywność

Wdrożenie zoptymalizowanych strategii rozmieszczania pól reticle zaowocowało ogromnym, 250-procentowym wzrostem przepustowości sieci w porównaniu do tradycyjnych bazowych rozwiązań 2D mesh. Ten skok wydajności wynika głównie z redukcji zatorów sieciowych; dzięki zapewnieniu bardziej bezpośrednich ścieżek dla danych, system może jednocześnie przesyłać większe ilości informacji. W przypadku wielkich modeli językowych oznacza to, że wzorce komunikacyjne „all-reduce” i „all-to-all”, które często wstrzymują trening, mogą zostać ukończone w ułamku czasu.

Poza czystą prędkością, badania podkreślają znaczną poprawę w zakresie opóźnień i zrównoważonego zużycia energii.

- Redukcja opóźnień: Opóźnienia w komunikacji zostały obniżone nawet o 36%, co pozwala na szybszą synchronizację wag modelu.

- Efektywność energetyczna: Energia wymagana na każdy przesłany bajt spadła nawet o 38%, co jest kluczowym wskaźnikiem wpływu AI na środowisko.

- Niezawodność systemu: Zmniejszając liczbę przeskoków i dystans elektryczny, który muszą pokonać dane, badacze poprawili również ogólną solidność struktury komunikacyjnej.

Implikacje dla branży: od Cerebras po superukłady przyszłości

Badania te stanowią mapę drogową dla przyszłości produkcji półprzewodników, wykraczając poza ograniczenia pojedynczych chipów GPU. Podczas gdy firmy takie jak Cerebras Systems udowodniły już opłacalność silników w skali wafla, prace Torstena Hoeflera i jego zespołu w ETH Zurich sugerują, że jesteśmy dopiero na początku tego, co możliwe. Wykorzystując wiązanie wafer-on-wafer i zaawansowane projektowanie topologii, przyszłe superukłady mogą pomieścić biliony tranzystorów w jednej obudowie, dostarczając sprzęt niezbędny do trenowania modeli znacznie większych niż GPT-4.

Przejście w kierunku zintegrowanej AI w skali wafla prawdopodobnie zdefiniuje na nowo konkurencję na rynku sprzętu AI. W miarę jak popyt na modele LLM gwałtownie rośnie, zdolność do minimalizacji zużycia energii przy jednoczesnej maksymalizacji przepustowości stanie się główną przewagą konkurencyjną. Przejście od budowania „klastrów chipów” do „systemów w skali wafla” stanowi fundamentalną zmianę w sposobie myślenia o architekturze komputerowej, obiecując przyszłość, w której fizyczny rozmiar naszego sprzętu będzie jedynym ograniczeniem dla inteligencji naszych modeli.

Comments

No comments yet. Be the first!