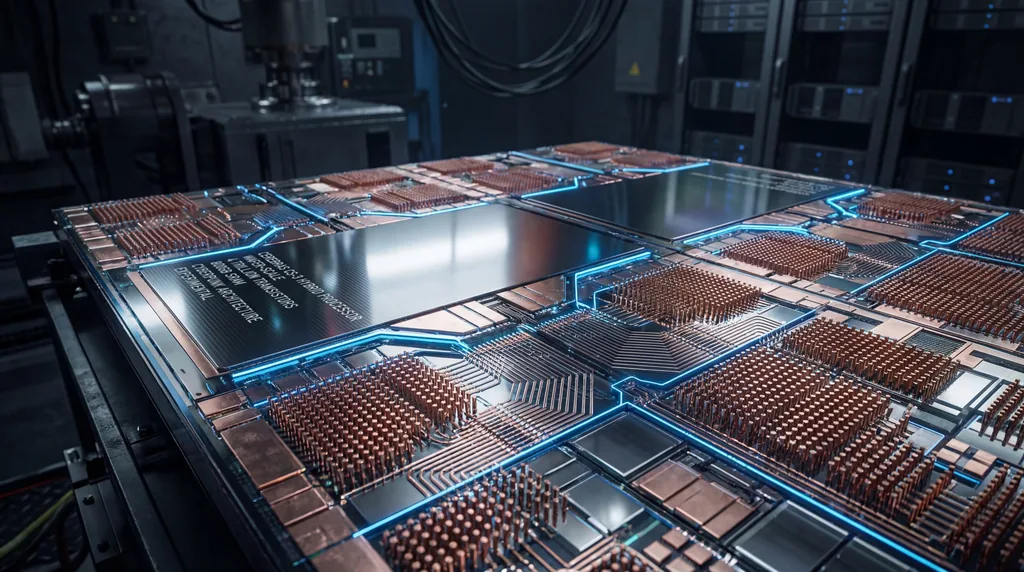

晶圆级 AI 集成通过将数十万个处理器核心和海量分布式内存整合到单个连续的硅表面上,解决了大语言模型(LLM)中的数据移动瓶颈。这种架构转变消除了传统多 GPU 集群中存在的“带宽墙”问题,在传统集群中,当数据跨越芯片边界时,通信速度会大幅下降。通过利用晶圆对晶圆(WoW)混合键合技术,研究人员实现了超高带宽互连,允许数据在整个系统中无缝流动,从而支持现代大语言模型(LLM)所需的大规模并行处理。

现代 AI 中的数据移动瓶颈

扩展大语言模型的主要瓶颈已从原始计算吞吐量转向芯片间数据移动的物理限制。在传统的性能计算集群(例如使用 NVIDIA DGX 系统的集群)中,单个 GPU 受限于与相邻处理器通信所需的物理引脚和布线。这创造了一道“通信墙”,其中芯片间移动数据的能量成本和延迟成为训练时间和推理效率的决定性因素。

在基于 Transformer 的模型训练同步阶段,互连延迟会产生显著的开销。随着模型增长到数万亿参数,频繁进行“All-reduce”操作(即在所有处理节点间共享梯度)的需求使传统网络硬件承压。这催生了“后 GPU”时代的研究,计算机科学家正寻求将整个硅晶圆视为一个统一的超级芯片,以维持下一代生成式 AI 所需的高速数据流。

什么是 Cerebras 晶圆级引擎,它是如何工作的?

Cerebras 晶圆级引擎(WSE)是一个巨大的晶圆级系统,它将数十万个 AI 优化核心和数 GB 的片上 SRAM 集成到单块硅片上。通过绕过将晶圆切割成微小独立芯片的传统工艺,WSE 在整个 215mm x 215mm 的表面上保留了硅制造工艺固有的高带宽布线。这种设计实现了一种网格架构(mesh architecture),支持超低延迟通信,这对于大规模执行大语言模型推理等受限于内存的操作至关重要。

WSE 通过利用专门的并行策略(如 MeshGEMM 和 MeshGEMV)来优化分布式内存访问。在标准 GPU 中,高带宽内存(HBM)位于处理器外部,形成了瓶颈;然而,晶圆级方法将内存直接放置在计算核心旁边。这种架构使系统能够管理模型预填充和 Token 生成所需的海量数据移动,而无需从外部组件获取数据的高能耗且缓慢的过程,从而为 AI 工作负载带来数个数量级的性能提升。

晶圆级集成与混合键合详解

晶圆对晶圆(WoW)混合键合是一种前沿制造技术,它垂直堆叠两个硅晶圆以创建高密度 3D 互连。与使用微凸点或焊料连接芯片的传统封装方法不同,混合键合直接将两个晶圆的铜焊盘融合在一起。这极大地增加了每平方毫米的连接点数量,有效地将处理单元(PE)之间的可用通信面积增加了一倍或两倍,并允许在 Wafer-Scale AI 系统中实现更复杂的网络拓扑。

- 增加的互连密度:混合键合允许在晶圆表面建立数百万个垂直连接。

- 降低寄生电容:直接的铜对铜界面降低了传输比特所需的电阻和能量。

- 增强热管理:结合先进的液冷技术,堆叠晶圆可以改善散热路径。

- 曝光场集成:该工艺允许在构成晶圆的矩形“曝光场(reticles)”(芯片制造的基本单位)之间进行无缝通信。

物理曝光场布局如何影响晶圆级芯片的网络拓扑?

物理曝光场(reticle)的放置决定了可实现的网络拓扑,它定义了高速片上布线必须转换为场间或晶圆间链路的边界。在标准的 Wafer-Scale AI 设计中,光刻工艺限制了单个功能单元(曝光场)的大小,需要步进模式来覆盖整个晶圆。包括 Luca Benini、Torsten Hoefler 和 Maciej Besta 在内的研究人员发现,这些曝光场的排列方式(无论是完美堆叠还是错位偏移)决定了数据必须经过的路径,从而直接影响延迟和吞吐量。

复杂的放置策略可以显著减少远程处理核心之间的“跳数(hop count)”。研究团队调查了四种主要配置:Aligned(对齐)、Interleaved(交错)、Rotated(旋转)和 Contoured(轮廓)。通过在混合键合过程中战略性地移动或旋转曝光场,他们能够创建在标准 2D 网格中不可能实现的快捷路径。例如,“Contoured”布局允许网络遵循晶圆自然的圆形形状,优化边缘硅片的使用,并为深度学习任务创建更高效的全局通信网络。

拓扑优化:四种曝光场放置策略

晶圆级网络的基准通常是 2D 网格,它受限于其僵化的网格状连通性。虽然 2D 网格可以运行,但当数据必须从晶圆的一侧传输到另一侧时,它会面临高延迟。为了解决这个问题,Hoefler 及其同事提出的研究表明,可以操纵晶圆的物理排列来为数据创建“快速通道”。Aligned 和 Interleaved 策略侧重于简化两个键合晶圆之间的垂直连接,以确保每个处理核心在相对层上都有一个直接伙伴。

像 Rotated 和 Contoured 这样先进的配置代表了高性能网络设计的突破。Rotated 策略涉及在键合前将一个晶圆旋转 90 度,这将物理布局转换为高基数(high-radix)网络。这种配置允许跨越晶圆的“长程”跳跃,而无需增加额外的物理布线。这些优化的拓扑结构确保网络能够处理稀疏 AI 模型中常见的零散数据模式,提供了一种能够适应不同神经网络架构的灵活基础设施。

量化收益:性能与效率

与传统的 2D 网格基准相比,优化后的曝光场放置策略使网络吞吐量大幅提升了 250%。这种性能飞跃主要归功于网络拥塞的减少;通过为数据提供更多直接路径,系统可以同时移动更大容量的信息。对于大语言模型,这意味着通常会拖慢训练进度的“All-reduce”和“All-to-all”通信模式可以在更短的时间内完成。

除了原始速度外,该研究还强调了在延迟和能源可持续性方面的显著改进。

- 延迟降低:通信延迟缩减了高达 36%,从而实现了更快的模型权重同步。

- 能源效率:每传输一个字节所需的能量降低了高达 38%,这是衡量 AI 环境影响的关键指标。

- 系统可靠性:通过减少跳数和数据必须经过的电气距离,研究人员还提高了通信架构的整体稳健性。

行业影响:从 Cerebras 到未来的超级芯片

这项研究为半导体制造的未来提供了路线图,跨越了单个 GPU 芯片的限制。虽然像 Cerebras Systems 这样的公司已经证明了晶圆级引擎的可行性,但 Torsten Hoefler 及其在 ETH Zurich 的团队的工作表明,我们才刚刚开启无限可能。通过利用晶圆对晶圆键合和先进的拓扑设计,未来的超级芯片可以在单个封装中容纳数万亿个晶体管,为训练比 GPT-4 大得多的模型提供必要的硬件基础。

向集成晶圆级 AI 的转变可能会重新定义 AI 硬件市场的竞争。随着对 LLM 的需求持续飙升,在最大化吞吐量的同时最小化能耗的能力将成为核心竞争优势。从构建“芯片集群”向“晶圆级系统”的转变,代表了我们思考计算机架构方式的根本改变,预示着一个物理硬件尺寸将成为模型智能唯一限制的未来。

Comments

No comments yet. Be the first!