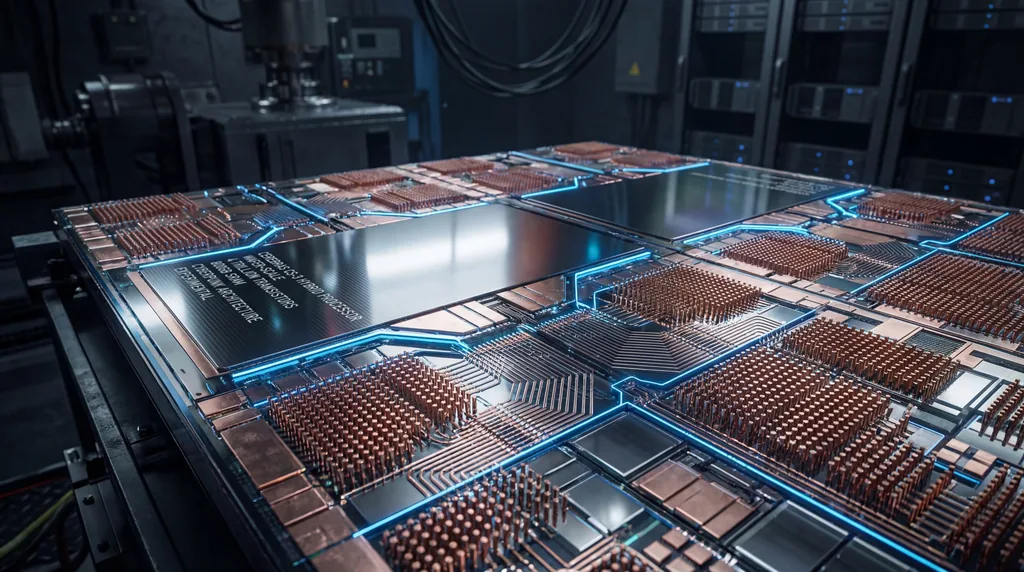

웨이퍼 스케일 AI 통합은 수십만 개의 프로세서 코어와 대규모 분산 메모리를 단일한 연속 실리콘 표면에 통합함으로써 LLM의 데이터 이동 병목 현상을 해결합니다. 이러한 아키텍처 변화는 데이터가 칩 경계를 넘을 때 통신 속도가 급격히 떨어지는 기존 멀티 GPU 클러스터의 "대역폭 벽(bandwidth wall)" 문제를 해결합니다. 연구진은 웨이퍼 온 웨이퍼(WoW) 하이브리드 본딩을 활용하여 초고대역폭 인터커넥트를 구현함으로써 전체 시스템에 걸쳐 원활한 데이터 흐름을 가능하게 했으며, 이는 현대 거대 언어 모델(LLM)에 필요한 대규모 병렬 처리를 용이하게 합니다.

현대 AI의 데이터 이동 병목 현상

거대 언어 모델 확장의 주요 병목 현상은 원시 연산 처리량에서 개별 칩 간 데이터 이동의 물리적 한계로 옮겨갔습니다. NVIDIA DGX 시스템을 사용하는 것과 같은 기존의 고성능 컴퓨팅 클러스터에서 개별 GPU는 인접한 프로세서와 통신하는 데 필요한 물리적 핀과 배선에 의해 제한됩니다. 이는 칩 간에 데이터를 이동시키는 데 드는 에너지 비용과 지연 시간이 학습 시간 및 추론 효율성의 지배적인 요인이 되는 "통신 벽"을 형성합니다.

인터커넥트 지연 시간은 트랜스포머 기반 모델 학습의 동기화 단계에서 상당한 오버헤드를 발생시킵니다. 모델이 수조 개의 파라미터 규모로 성장함에 따라, 모든 프로세싱 노드 간에 그래디언트를 공유하는 빈번한 "올 리듀스(all-reduce)" 작업의 필요성이 기존 네트워킹 하드웨어에 부담을 줍니다. 이로 인해 컴퓨터 과학자들이 차세대 생성형 AI에 필요한 고속 데이터 흐름을 유지하기 위해 전체 실리콘 웨이퍼를 하나의 통합된 슈퍼 칩으로 취급하는 방법을 모색하는 "포스트 GPU" 연구 시대가 열렸습니다.

Cerebras의 웨이퍼 스케일 엔진이란 무엇이며 어떻게 작동하나요?

Cerebras의 웨이퍼 스케일 엔진(WSE)은 수십만 개의 AI 최적화 코어와 기가바이트급 온칩 SRAM을 단일 실리콘 조각에 통합한 거대한 시스템 온 웨이퍼입니다. 웨이퍼를 작은 개별 칩으로 절단하는 전통적인 공정을 우회함으로써, WSE는 215mm x 215mm 전체 표면에 걸쳐 실리콘 제조 공정 고유의 고대역폭 배선을 유지합니다. 이러한 설계는 대규모 거대 언어 모델 추론과 같은 메모리 집약적(memory-bound) 작업을 실행하는 데 필수적인 초저지연 통신을 지원하는 메시 아키텍처(mesh architecture)를 가능하게 합니다.

WSE는 MeshGEMM 및 MeshGEMV와 같은 특화된 병렬 처리 전략을 활용하여 분산 메모리 액세스를 최적화하는 방식으로 작동합니다. 표준 GPU에서는 고대역폭 메모리(HBM)가 프로세서 외부에 위치하여 병목 현상을 일으키지만, 웨이퍼 스케일 방식은 메모리를 연산 코어 바로 옆에 배치합니다. 이 아키텍처를 통해 시스템은 외부 구성 요소에서 데이터를 가져오는 전력 소모가 크고 느린 과정 없이 모델 프리필링(prefilling) 및 토큰 생성에 필요한 대규모 데이터 이동을 관리할 수 있으며, 그 결과 AI 워크로드에서 수십 배 더 빠른 성능을 제공합니다.

웨이퍼 스케일 통합 및 하이브리드 본딩 설명

웨이퍼 온 웨이퍼(WoW) 하이브리드 본딩은 두 개의 실리콘 웨이퍼를 수직으로 적층하여 고밀도 3D 인터커넥트를 만드는 최첨단 제조 기술입니다. 마이크로 범프나 솔더를 사용하여 칩을 연결하는 기존 패키징 방식과 달리, 하이브리드 본딩은 두 웨이퍼의 구리 패드를 직접 융합합니다. 이는 제곱밀리미터당 훨씬 더 많은 연결 지점을 제공하여 프로세싱 엘리먼트(PE) 간의 가용 통신 면적을 사실상 두 배 또는 세 배로 늘려주며, 웨이퍼 스케일 AI 시스템에서 훨씬 더 복잡한 네트워크 토폴로지를 구현할 수 있게 합니다.

- 인터커넥트 밀도 증가: 하이브리드 본딩을 통해 웨이퍼 표면 전체에 수백만 개의 수직 연결이 가능해집니다.

- 기생 커패시턴스 감소: 직접적인 구리 대 구리 인터페이스는 전기 저항과 비트 전송에 필요한 에너지를 낮춥니다.

- 향상된 열 관리: 웨이퍼를 적층하면 고급 액체 냉각 기술과 결합될 때 열 방산 경로를 개선할 수 있습니다.

- 레티클 통합: 이 공정은 웨이퍼를 구성하는 직사각형 "레티클(reticles)"(칩 제조의 기본 단위) 간의 원활한 통신을 가능하게 합니다.

물리적 레티클 배치가 웨이퍼 스케일 칩의 네트워크 토폴로지에 어떤 영향을 미치나요?

물리적 레티클 배치는 고속 온칩 배선이 레티클 간 또는 웨이퍼 간 링크로 전환되어야 하는 경계를 정의함으로써 구현 가능한 네트워크 토폴로지를 결정합니다. 표준 웨이퍼 스케일 AI 설계에서 리소그래피 공정은 단일 기능 단위(레티클)의 크기를 제한하므로, 전체 웨이퍼를 덮기 위해 스테핑 패턴이 필요합니다. Luca Benini, Torsten Hoefler, Maciej Besta를 포함한 연구진은 이러한 레티클이 정렬되는 방식(완벽하게 적층되는지 또는 어긋나게 배치되는지)이 데이터 이동 경로를 결정하며, 지연 시간과 처리량에 직접적인 영향을 미친다는 것을 발견했습니다.

정교한 배치 전략은 멀리 떨어진 프로세싱 코어 간의 "홉 수(hop count)"를 크게 줄일 수 있습니다. 연구팀은 Aligned, Interleaved, Rotated, Contoured의 네 가지 주요 구성을 조사했습니다. 하이브리드 본딩 과정에서 레티클을 전략적으로 이동하거나 회전시킴으로써 표준 2D 메시에서는 불가능한 단축 경로를 만들 수 있었습니다. 예를 들어, "Contoured" 배치는 네트워크가 웨이퍼의 자연스러운 원형 모양을 따르도록 하여 엣지 케이스 실리콘의 활용을 최적화하고 딥러닝 작업을 위한 보다 효율적인 글로벌 통신 구조를 형성합니다.

토폴로지 최적화: 네 가지 레티클 배치 전략

웨이퍼 스케일 네트워크의 기준은 일반적으로 2D 메시이며, 이는 경직된 격자형 연결성으로 인해 한계가 있습니다. 2D 메시는 기능적으로는 작동하지만, 데이터가 웨이퍼의 한쪽 끝에서 다른 쪽 끝으로 이동해야 할 때 높은 지연 시간이 발생합니다. 이를 해결하기 위해 Hoefler와 동료들의 연구는 웨이퍼의 물리적 배열을 조작하여 데이터의 "급행 차선"을 만들 수 있다고 제안합니다. Aligned 및 Interleaved 전략은 본딩된 두 웨이퍼 사이의 수직 연결을 단순화하여 모든 프로세싱 코어가 반대편 레이어에 직접적인 파트너를 갖도록 하는 데 중점을 둡니다.

Rotated 및 Contoured 배치와 같은 고급 구성은 고성능 네트워크 설계의 획기적인 발전을 의미합니다. Rotated 전략은 본딩 전 한쪽 웨이퍼를 90도 회전시키는 것으로, 물리적 레이아웃을 하이 래딕스(high-radix) 네트워크로 변환합니다. 이 구성은 추가적인 물리적 배선 없이도 웨이퍼 전체에 걸친 "장거리" 홉을 가능하게 합니다. 이러한 최적화된 토폴로지는 네트워크가 희소(sparse) AI 모델에서 흔히 볼 수 있는 불규칙한 데이터 패턴을 처리할 수 있도록 보장하며, 다양한 신경망 아키텍처에 적응할 수 있는 유연한 인프라를 제공합니다.

이득 수치화: 성능 및 효율성

최적화된 레티클 배치 전략을 구현한 결과, 기존 2D 메시 기준 대비 네트워크 처리량이 250%나 대폭 증가했습니다. 이러한 성능 향상은 주로 네트워크 혼잡의 감소 덕분입니다. 데이터에 더 많은 직접 경로를 제공함으로써 시스템은 더 많은 양의 정보를 동시에 이동시킬 수 있습니다. 거대 언어 모델의 경우, 이는 종종 학습을 지체시키는 "올 리듀스" 및 "올 투 올(all-to-all)" 통신 패턴을 훨씬 짧은 시간 안에 완료할 수 있음을 의미합니다.

단순한 속도 향상을 넘어, 이번 연구는 지연 시간과 에너지 지속 가능성 측면에서도 상당한 개선을 보여줍니다.

- 지연 시간 단축: 통신 지연이 최대 36%까지 줄어들어 모델 가중치의 더 빠른 동기화가 가능해졌습니다.

- 에너지 효율성: 전송된 바이트당 필요한 에너지가 최대 38% 감소했으며, 이는 AI의 환경적 영향 측면에서 중요한 지표입니다.

- 시스템 신뢰성: 홉 수와 데이터가 이동해야 하는 전기적 거리를 줄임으로써 연구진은 통신 구조의 전반적인 견고성 또한 향상시켰습니다.

산업계에 미치는 영향: Cerebras에서 미래의 슈퍼 칩까지

이 연구는 개별 GPU 칩의 한계를 뛰어넘는 반도체 제조의 미래 로드맵을 제시합니다. Cerebras Systems와 같은 기업들이 이미 웨이퍼 스케일 엔진의 실용성을 입증했지만, Torsten Hoefler와 ETH Zurich 연구팀의 작업은 우리가 가능성의 시작 단계에 있음을 시사합니다. 웨이퍼 온 웨이퍼 본딩과 고급 토폴로지 설계를 활용함으로써 미래의 슈퍼 칩은 단일 패키지에 수조 개의 트랜지스터를 탑재할 수 있게 되며, GPT-4보다 훨씬 거대한 모델을 학습시키는 데 필요한 하드웨어를 제공하게 될 것입니다.

통합된 웨이퍼 스케일 AI로의 전환은 AI 하드웨어 시장의 경쟁 구도를 재정의할 것으로 보입니다. LLM에 대한 수요가 계속해서 급증함에 따라 처리량을 극대화하면서 에너지 소비를 최소화하는 능력이 주요 경쟁 우위가 될 것입니다. "칩 클러스터" 구축에서 "웨이퍼 스케일 시스템"으로의 전환은 컴퓨터 아키텍처에 대한 우리의 생각 방식을 근본적으로 바꾸는 것이며, 하드웨어의 물리적 크기만이 모델 지능의 유일한 한계가 되는 미래를 약속합니다.

Comments

No comments yet. Be the first!