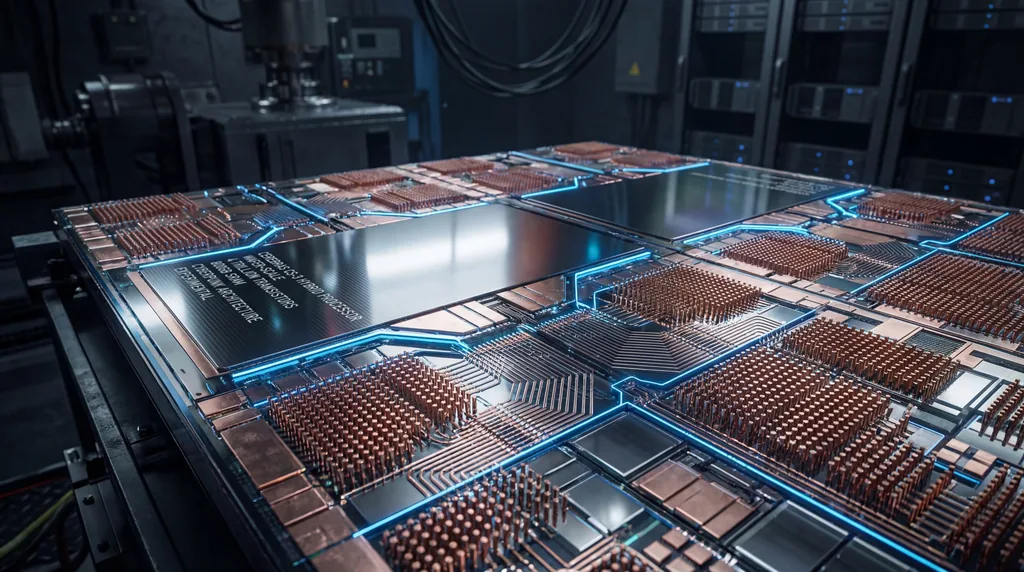

A integração de IA em escala de wafer (Wafer-Scale AI) aborda os gargalos de movimento de dados em LLMs ao consolidar centenas de milhares de núcleos de processadores e memória distribuída massiva em uma única superfície de silício contínua. Esta mudança arquitetônica elimina o "muro de largura de banda" (bandwidth wall) encontrado em clusters tradicionais de múltiplas GPUs, onde as velocidades de comunicação caem significativamente quando os dados cruzam as fronteiras do chip. Ao utilizar a ligação híbrida wafer-on-wafer (WoW), pesquisadores permitiram interconexões de ultra-alta largura de banda que possibilitam um fluxo de dados contínuo por todo o sistema, facilitando o processamento paralelo massivo exigido pelos modernos Grandes Modelos de Linguagem (LLMs).

O Gargalo do Movimento de Dados na IA Moderna

O principal gargalo para o escalonamento de Grandes Modelos de Linguagem mudou da capacidade computacional bruta para as limitações físicas do movimento de dados entre chips individuais. Em clusters de computação de alto desempenho convencionais, como aqueles que utilizam sistemas NVIDIA DGX, as GPUs individuais são limitadas pelos pinos físicos e pela fiação necessária para se comunicarem com processadores vizinhos. Isso cria uma "parede de comunicação" onde o custo energético e a latência do deslocamento de dados entre chips tornam-se os fatores dominantes no tempo de treinamento e na eficiência de inferência.

A latência de interconexão cria uma sobrecarga significativa durante as fases de sincronização do treinamento de modelos baseados em Transformer. À medida que os modelos crescem para trilhões de parâmetros, a necessidade de operações frequentes de "all-reduce" — onde os gradientes são compartilhados entre todos os nós de processamento — sobrecarrega o hardware de rede tradicional. Isso levou a uma era de pesquisa "Pós-GPU", na qual cientistas da computação buscam maneiras de tratar um wafer de silício inteiro como um único superchip unificado para manter o fluxo de dados de alta velocidade necessário para a próxima geração de IA generativa.

O que é o wafer-scale engine da Cerebras e como ele funciona?

O wafer-scale engine (WSE) da Cerebras é um sistema massivo em wafer que integra centenas de milhares de núcleos otimizados para IA e gigabytes de SRAM on-chip em uma única peça de silício. Ao contornar o processo tradicional de corte de wafers em pequenos chips individuais, o WSE mantém a fiação de alta largura de banda inerente ao processo de fabricação de silício em toda a superfície de 215 mm x 215 mm. Este design permite uma arquitetura de malha (mesh architecture) que suporta comunicação de ultra-baixa latência, o que é crítico para executar operações limitadas por memória, como a inferência de Grandes Modelos de Linguagem em escala.

O WSE funciona aproveitando estratégias de paralelismo especializadas, como MeshGEMM e MeshGEMV, para otimizar o acesso à memória distribuída. Em uma GPU padrão, a memória de alta largura de banda (HBM) está localizada fora do processador, criando um gargalo; no entanto, a abordagem em escala de wafer coloca a memória diretamente adjacente aos núcleos de computação. Essa arquitetura permite que o sistema gerencie o movimento massivo de dados exigido para o preenchimento de modelos (prefilling) e a geração de tokens sem o processo lento e de alto consumo de energia de buscar dados em componentes externos, resultando em um desempenho ordens de magnitude mais rápido para cargas de trabalho de IA.

Integração em Escala de Wafer e Ligação Híbrida Explicadas

A ligação híbrida wafer-on-wafer (WoW) é uma técnica de fabricação de ponta que empilha verticalmente dois wafers de silício para criar uma interconexão 3D de alta densidade. Ao contrário dos métodos tradicionais de encapsulamento que usam micro-bumps ou solda para conectar chips, a ligação híbrida funde os contatos de cobre de dois wafers diretamente. Isso fornece um número significativamente maior de pontos de conexão por milímetro quadrado, efetivamente dobrando ou triplicando a área de comunicação disponível entre os elementos de processamento (PEs) e permitindo topologias de rede muito mais complexas em sistemas de Wafer-Scale AI.

- Aumento da Densidade de Interconexão: A ligação híbrida permite milhões de conexões verticais em toda a superfície do wafer.

- Redução da Capacitância Parasitária: A interface direta cobre-com-cobre reduz a resistência elétrica e a energia necessária para transmitir bits.

- Gestão Térmica Aprimorada: O empilhamento de wafers pode melhorar os caminhos de dissipação de calor quando combinado com resfriamento líquido avançado.

- Integração de Retículos: O processo permite uma comunicação contínua entre os "retículos" retangulares (as unidades básicas da fabricação de chips) que compõem o wafer.

Como o posicionamento físico do retículo afeta a topologia da rede em chips de escala de wafer?

O posicionamento físico do retículo dita a topologia de rede alcançável ao definir as fronteiras onde a fiação on-chip de alta velocidade deve transitar para links entre retículos ou entre wafers. Em um design de Wafer-Scale AI padrão, o processo de litografia limita o tamanho de uma única unidade funcional (o retículo), exigindo um padrão de repetição (stepping) para cobrir todo o wafer. Os pesquisadores, incluindo Luca Benini, Torsten Hoefler e Maciej Besta, descobriram que a maneira como esses retículos são alinhados — se estão perfeitamente empilhados ou deslocados — determina o caminho que os dados devem percorrer, impactando diretamente a latência e a taxa de transferência.

Estratégias sofisticadas de posicionamento podem reduzir significativamente a "contagem de saltos" (hop count) entre núcleos de processamento distantes. A equipe de pesquisa investigou quatro configurações primárias: Alinhado, Intercalado, Rotacionado e Contornado. Ao deslocar ou rotacionar estrategicamente os retículos durante o processo de ligação híbrida, eles conseguiram criar caminhos de atalho que seriam impossíveis em uma malha 2D padrão. Por exemplo, um posicionamento "Contornado" permite que a rede siga a forma circular natural do wafer, otimizando o uso do silício nas extremidades e criando um tecido de comunicação global mais eficiente para tarefas de aprendizado profundo.

Otimizando a Topologia: As Quatro Estratégias de Posicionamento de Retículos

A base para redes em escala de wafer é tipicamente uma malha 2D, que é limitada por sua conectividade rígida em forma de grade. Embora funcional, a malha 2D sofre com alta latência quando os dados precisam viajar de um lado do wafer para o outro. Para resolver isso, a pesquisa apresentada por Hoefler e seus colegas sugere que o arranjo físico dos wafers pode ser manipulado para criar "vias expressas" para os dados. As estratégias Alinhado e Intercalado focam em simplificar as conexões verticais entre dois wafers ligados para garantir que cada núcleo de processamento tenha um parceiro direto na camada oposta.

Configurações avançadas, como os posicionamentos Rotacionado e Contornado, representam um avanço no design de redes de alto desempenho. A estratégia Rotacionado envolve girar um wafer em 90 graus antes da ligação, o que transforma o layout físico em uma rede de alto radix. Esta configuração permite saltos de "longo alcance" através do wafer sem adicionar fiação física extra. Essas topologias otimizadas garantem que a rede possa lidar com os padrões de dados erráticos frequentemente vistos em modelos de IA esparsos, fornecendo uma infraestrutura flexível que pode se adaptar a diferentes arquiteturas de redes neurais.

Quantificando os Ganhos: Desempenho e Eficiência

A implementação de estratégias otimizadas de posicionamento de retículos resultou em um aumento massivo de 250% na taxa de transferência da rede em comparação com as bases de malha 2D tradicionais. Esse salto de desempenho deve-se principalmente à redução no congestionamento da rede; ao fornecer caminhos mais diretos para os dados, o sistema pode mover volumes maiores de informações simultaneamente. Para Grandes Modelos de Linguagem, isso significa que os padrões de comunicação "all-reduce" e "all-to-all", que frequentemente interrompem o treinamento, podem ser concluídos em uma fração do tempo.

Além da velocidade bruta, a pesquisa destaca melhorias significativas na latência e na sustentabilidade energética.

- Redução de Latência: Os atrasos de comunicação foram reduzidos em até 36%, permitindo uma sincronização mais rápida dos pesos do modelo.

- Eficiência Energética: A energia necessária por byte transmitido diminuiu em até 38%, uma métrica crítica para o impacto ambiental da IA.

- Confiabilidade do Sistema: Ao reduzir o número de saltos e a distância elétrica que os dados devem percorrer, os pesquisadores também melhoraram a robustez geral do tecido de comunicação.

Implicações para a Indústria: Da Cerebras aos Superchips do Futuro

Esta pesquisa fornece um roteiro para o futuro da fabricação de semicondutores, indo além dos limites dos chips de GPU individuais. Embora empresas como a Cerebras Systems já tenham comprovado a viabilidade dos motores em escala de wafer, o trabalho de Torsten Hoefler e sua equipe na ETH Zurique sugere que estamos apenas no começo do que é possível. Ao utilizar a ligação wafer-on-wafer e o design avançado de topologia, os futuros superchips poderiam abrigar trilhões de transistores em um único encapsulamento, fornecendo o hardware necessário para treinar modelos muito maiores que o GPT-4.

A mudança em direção à Wafer-Scale AI integrada provavelmente redefinirá a competição no mercado de hardware de IA. À medida que a demanda por LLMs continua a disparar, a capacidade de minimizar o consumo de energia enquanto se maximiza a taxa de transferência se tornará a principal vantagem competitiva. A transição da construção de "clusters de chips" para "sistemas em escala de wafer" representa uma mudança fundamental em como pensamos sobre a arquitetura de computadores, prometendo um futuro onde o tamanho físico do nosso hardware seja o único limite para a inteligência de nossos modelos.

Comments

No comments yet. Be the first!