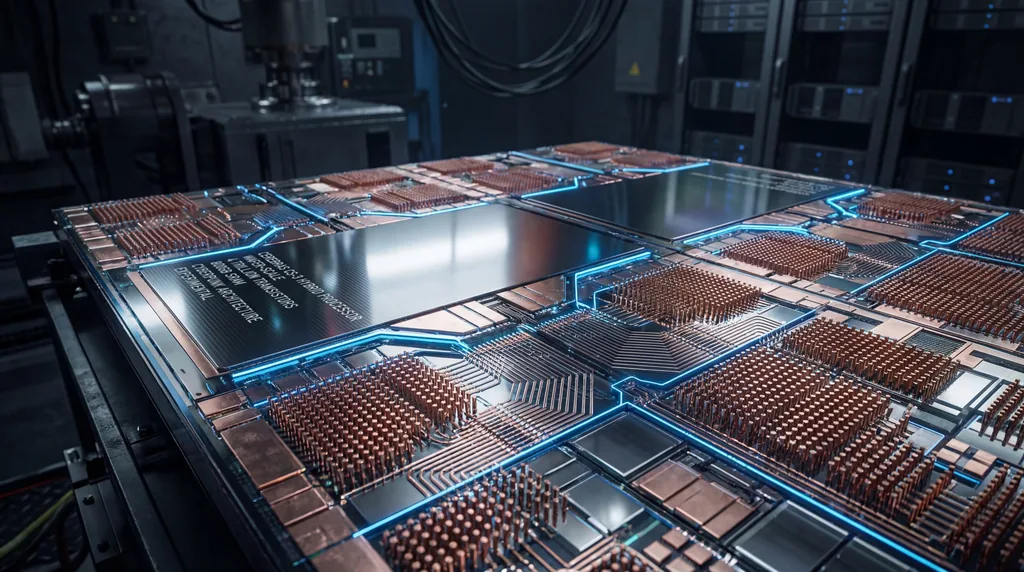

L'integrazione dell'AI Wafer-Scale affronta i colli di bottiglia nel movimento dei dati nei LLM consolidando centinaia di migliaia di core di processori e una massiccia memoria distribuita su un'unica superficie di silicio continua. Questo spostamento architetturale elimina il "muro della larghezza di banda" riscontrato nei tradizionali cluster multi-GPU, dove le velocità di comunicazione diminuiscono drasticamente quando i dati attraversano i confini dei chip. Utilizzando l'hybrid bonding wafer-on-wafer (WoW), i ricercatori hanno abilitato interconnessioni ad altissima larghezza di banda che consentono un flusso di dati senza interruzioni attraverso l'intero sistema, facilitando l'elaborazione parallela massiccia richiesta dai moderni Large Language Models (LLM).

Il collo di bottiglia del movimento dei dati nell'AI moderna

Il principale collo di bottiglia per la scalabilità dei Large Language Models si è spostato dal throughput computazionale grezzo ai limiti fisici del movimento dei dati tra i singoli chip. Nei cluster di calcolo ad alte prestazioni convenzionali, come quelli che utilizzano i sistemi NVIDIA DGX, le singole GPU sono limitate dai pin fisici e dai cablaggi necessari per comunicare con i processori vicini. Ciò crea un "muro della comunicazione" in cui il costo energetico e la latenza dello spostamento dei dati tra i chip diventano i fattori dominanti nel tempo di addestramento e nell'efficienza dell'inferenza.

La latenza di interconnessione crea un overhead significativo durante le fasi di sincronizzazione dell'addestramento dei modelli basati su Transformer. Poiché i modelli crescono fino a trilioni di parametri, la necessità di frequenti operazioni "all-reduce" — in cui i gradienti vengono condivisi tra tutti i nodi di elaborazione — mette a dura prova l'hardware di rete tradizionale. Ciò ha portato a un'era di ricerca "Post-GPU", in cui gli informatici cercano modi per trattare un intero wafer di silicio come un unico super-chip unificato per mantenere il flusso di dati ad alta velocità necessario per la prossima generazione di AI generativa.

Cos'è il wafer-scale engine di Cerebras e come funziona?

Il wafer-scale engine (WSE) di Cerebras è un enorme sistema su wafer che integra centinaia di migliaia di core ottimizzati per l'AI e gigabyte di SRAM on-chip su un unico pezzo di silicio. Evitando il processo tradizionale di taglio dei wafer in piccoli chip individuali, il WSE mantiene il cablaggio ad alta larghezza di banda inerente al processo di produzione del silicio su l'intera superficie di 215 mm x 215 mm. Questo design consente un'architettura mesh che supporta comunicazioni a bassissima latenza, fondamentali per l'esecuzione su scala di operazioni limitate dalla memoria (memory-bound) come l'inferenza dei Large Language Models.

Il WSE funziona sfruttando strategie di parallelismo specializzate, come MeshGEMM e MeshGEMV, per ottimizzare l'accesso alla memoria distribuita. In una GPU standard, la memoria ad alta larghezza di banda (HBM) si trova all'esterno del processore, creando un collo di bottiglia; tuttavia, l'approccio wafer-scale posiziona la memoria direttamente accanto ai core di calcolo. Questa architettura consente al sistema di gestire il massiccio movimento di dati richiesto per il prefilling del modello e la generazione di token senza il processo lento ed energivoro di recupero dei dati da componenti esterni, con una conseguente velocità di prestazioni superiore di ordini di grandezza per i carichi di lavoro AI.

Integrazione Wafer-Scale e Hybrid Bonding spiegati

L'hybrid bonding wafer-on-wafer (WoW) è una tecnica di produzione all'avanguardia che impila verticalmente due wafer di silicio per creare un'interconnessione 3D ad alta densità. A differenza dei metodi di packaging tradizionali che utilizzano micro-bump o saldature per collegare i chip, l'hybrid bonding fonde direttamente i pad di rame di due wafer. Ciò fornisce un numero significativamente maggiore di punti di connessione per millimetro quadrato, raddoppiando o triplicando efficacemente l'area di comunicazione disponibile tra gli elementi di elaborazione (PE) e consentendo topologie di rete molto più complesse nei sistemi AI Wafer-Scale.

- Maggiore densità di interconnessione: L'hybrid bonding consente milioni di connessioni verticali attraverso la superficie del wafer.

- Riduzione della capacità parassita: L'interfaccia diretta rame-rame riduce la resistenza elettrica e l'energia necessaria per trasmettere i bit.

- Gestione termica migliorata: L'impilamento dei wafer può migliorare i percorsi di dissipazione del calore se combinato con un raffreddamento a liquido avanzato.

- Integrazione dei reticoli: Il processo consente una comunicazione fluida tra i "reticoli" rettangolari (le unità di base della produzione di chip) che compongono il wafer.

In che modo il posizionamento fisico dei reticoli influisce sulla topologia di rete nei chip wafer-scale?

Il posizionamento fisico dei reticoli determina la topologia di rete realizzabile definendo i confini in cui il cablaggio on-chip ad alta velocità deve transire in collegamenti inter-reticolo o inter-wafer. In un design standard di AI Wafer-Scale, il processo litografico limita le dimensioni di una singola unità funzionale (il reticolo), richiedendo un pattern a step per coprire l'intero wafer. I ricercatori, tra cui Luca Benini, Torsten Hoefler e Maciej Besta, hanno scoperto che il modo in cui questi reticoli sono allineati — se perfettamente impilati o sfalsati — determina il percorso che i dati devono compiere, influenzando direttamente la latenza e il throughput.

Strategie di posizionamento sofisticate possono ridurre significativamente il "conteggio degli hop" tra core di elaborazione distanti. Il team di ricerca ha studiato quattro configurazioni primarie: Aligned, Interleaved, Rotated e Contoured. Spostando o ruotando strategicamente i reticoli durante il processo di hybrid bonding, sono stati in grado di creare percorsi scorciatoia che sarebbero impossibili in una mesh 2D standard. Ad esempio, un posizionamento "Contoured" consente alla rete di seguire la naturale forma circolare del wafer, ottimizzando l'uso del silicio nelle zone periferiche e creando un tessuto di comunicazione globale più efficiente per i compiti di deep learning.

Ottimizzazione della topologia: Le quattro strategie di posizionamento dei reticoli

La base per le reti wafer-scale è tipicamente una mesh 2D, limitata dalla sua connettività rigida a griglia. Sebbene funzionale, la mesh 2D soffre di un'elevata latenza quando i dati devono viaggiare da un lato all'altro del wafer. Per affrontare questo problema, la ricerca presentata da Hoefler e dai suoi colleghi suggerisce che la disposizione fisica dei wafer può essere manipolata per creare "corsie preferenziali" per i dati. Le strategie Aligned e Interleaved si concentrano sulla semplificazione delle connessioni verticali tra due wafer legati per garantire che ogni core di elaborazione abbia un partner diretto sullo strato opposto.

Configurazioni avanzate come i posizionamenti Rotated e Contoured rappresentano una svolta nel design di reti ad alte prestazioni. La strategia Rotated prevede la rotazione di un wafer di 90 gradi prima del bonding, il che trasforma il layout fisico in una rete ad alto radix. Questa configurazione consente salti a "lungo raggio" attraverso il wafer senza aggiungere cablaggi fisici extra. Queste topologie ottimizzate assicurano che la rete possa gestire i pattern di dati irregolari spesso visti nei modelli AI sparsi, fornendo un'infrastruttura flessibile in grado di adattarsi a diverse architetture di reti neurali.

Quantificare i guadagni: Prestazioni ed efficienza

L'implementazione di strategie ottimizzate di posizionamento dei reticoli ha portato a un massiccio aumento del 250% del throughput di rete rispetto ai baseline mesh 2D tradizionali. Questo salto prestazionale è dovuto principalmente alla riduzione della congestione di rete; fornendo percorsi più diretti per i dati, il sistema può spostare volumi maggiori di informazioni simultaneamente. Per i Large Language Models, ciò significa che i pattern di comunicazione "all-reduce" e "all-to-all", che spesso bloccano l'addestramento, possono essere completati in una frazione del tempo.

Oltre alla velocità pura, la ricerca evidenzia miglioramenti significativi nella latenza e nella sostenibilità energetica.

- Riduzione della latenza: I ritardi di comunicazione sono stati ridotti fino al 36%, consentendo una sincronizzazione più rapida dei pesi del modello.

- Efficienza energetica: L'energia richiesta per byte trasmesso è diminuita fino al 38%, una metrica critica per l'impatto ambientale dell'AI.

- Affidabilità del sistema: Riducendo il numero di hop e la distanza elettrica che i dati devono percorrere, i ricercatori hanno anche migliorato la robustezza complessiva del tessuto di comunicazione.

Implicazioni per l'industria: Da Cerebras ai futuri super-chip

Questa ricerca fornisce una tabella di marcia per il futuro della produzione di semiconduttori, andando oltre i limiti dei singoli chip GPU. Mentre aziende come Cerebras Systems hanno già dimostrato la fattibilità dei wafer-scale engine, il lavoro di Torsten Hoefler e del suo team all'ETH Zurich suggerisce che siamo solo all'inizio di ciò che è possibile. Utilizzando il bonding wafer-on-wafer e un design avanzato della topologia, i futuri super-chip potrebbero ospitare trilioni di transistor in un unico package, fornendo l'hardware necessario per addestrare modelli molto più grandi di GPT-4.

Il passaggio verso l'AI Wafer-Scale integrata ridefinirà probabilmente la competizione nel mercato dell'hardware AI. Mentre la domanda di LLM continua a salire alle stelle, la capacità di ridurre al minimo il consumo energetico massimizzando al contempo il throughput diventerà il principale vantaggio competitivo. La transizione dal costruire "cluster di chip" a "sistemi wafer-scale" rappresenta un cambiamento fondamentale nel modo in cui pensiamo all'architettura dei computer, promettendo un futuro in cui la dimensione fisica del nostro hardware sarà l'unico limite all'intelligenza dei nostri modelli.

Comments

No comments yet. Be the first!