Wafer-scale AI-integratie pakt knelpunten in de gegevensverplaatsing bij LLM's aan door honderdduizenden processorkernen en massaal gedistribueerd geheugen te consolideren op één enkel, ononderbroken siliciumoppervlak. Deze architecturale verschuiving elimineert de "bandbreedtemuur" die optreedt bij traditionele multi-GPU-clusters, waarbij communicatiesnelheden aanzienlijk dalen zodra gegevens de grenzen van de chip overschrijden. Door gebruik te maken van wafer-on-wafer (WoW) hybride bonding hebben onderzoekers ultra-hoge-bandbreedte-interconnects mogelijk gemaakt die een naadloze gegevensstroom door het hele systeem toelaten, wat de massale parallelle verwerking faciliteert die nodig is voor moderne Large Language Models (LLM's).

Het knelpunt van gegevensverplaatsing in moderne AI

Het primaire knelpunt voor het opschalen van Large Language Models is verschoven van pure rekenkracht naar de fysieke beperkingen van gegevensverplaatsing tussen individuele chips. In conventionele high-performance computing clusters, zoals die gebruikmaken van NVIDIA DGX-systemen, worden individuele GPU's beperkt door de fysieke pinnen en bedrading die nodig zijn om te communiceren met naburige processors. Dit creëert een "communicatiemuur" waarbij de energiekosten en latentie van het verplaatsen van gegevens tussen chips de dominante factoren worden in trainingstijd en efficiëntie van inferentie.

Interconnect-latentie zorgt voor aanzienlijke overhead tijdens de synchronisatiefases van de training van op Transformers gebaseerde modellen. Naarmate modellen groeien naar biljoenen parameters, zet de behoefte aan frequente "all-reduce"-operaties — waarbij gradiënten worden gedeeld over alle verwerkingsnodes — traditionele netwerkhardware onder druk. Dit heeft geleid tot een "Post-GPU"-tijdperk van onderzoek, waarin computerwetenschappers naar manieren zoeken om een volledige siliciumwafer als één enkele, verenigde superchip te behandelen om de snelle gegevensstroom te behouden die noodzakelijk is voor de volgende generatie generatieve AI.

Wat is de wafer-scale engine van Cerebras en hoe werkt het?

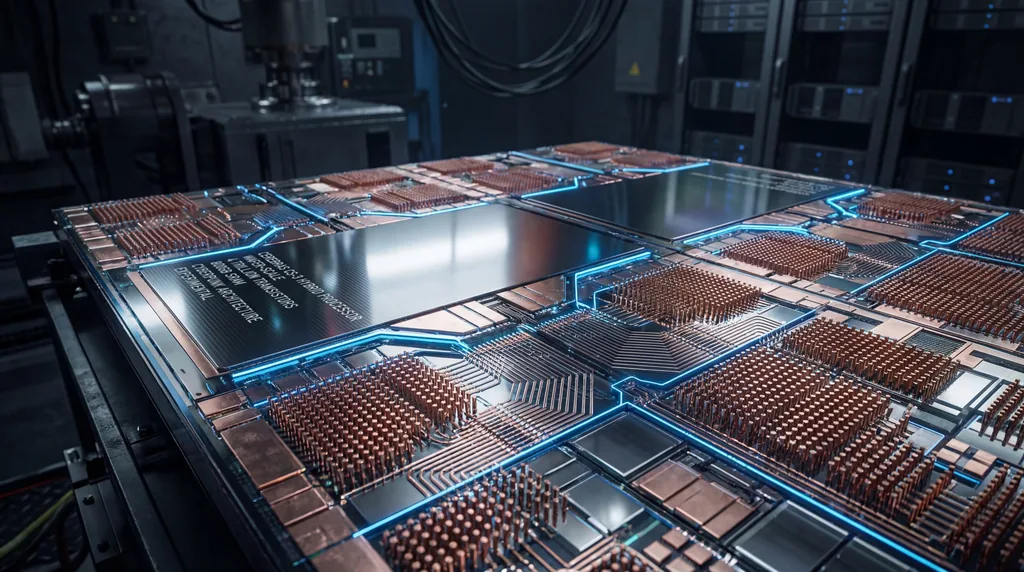

De wafer-scale engine (WSE) van Cerebras is een massief system-on-wafer dat honderdduizenden voor AI geoptimaliseerde kernen en gigabytes aan on-chip SRAM integreert op één enkel stuk silicium. Door het traditionele proces van het versnijden van wafers in kleine individuele chips te omzeilen, behoudt de WSE de voor het siliciumproductieproces inherente hoge-bandbreedte-bedrading over het gehele oppervlak van 215 mm x 215 mm. Dit ontwerp maakt een mesh-architectuur mogelijk die communicatie met ultra-lage latentie ondersteunt, wat essentieel is voor het op schaal uitvoeren van geheugenintensieve taken zoals de inferentie van Large Language Models.

De WSE functioneert door gebruik te maken van gespecialiseerde parallellismestrategieën, zoals MeshGEMM en MeshGEMV, om de toegang tot gedistribueerd geheugen te optimaliseren. In een standaard GPU bevindt het high-bandwidth memory (HBM) zich buiten de processor, wat een knelpunt vormt; de wafer-scale-benadering plaatst het geheugen echter direct naast de rekenkernen. Deze architectuur stelt het systeem in staat om de enorme gegevensverplaatsing te beheren die vereist is voor model-prefilling en token-generatie, zonder het energieverslindende en trage proces van het ophalen van gegevens uit externe componenten, wat resulteert in ordes van grootte snellere prestaties voor AI-workloads.

Wafer-scale integratie en hybride bonding uitgelegd

Wafer-on-wafer (WoW) hybride bonding is een geavanceerde productietechniek waarbij twee siliciumwafers verticaal worden gestapeld om een 3D-interconnect met hoge dichtheid te creëren. In tegenstelling tot traditionele verpakkingsmethoden die micro-bumps of soldeer gebruiken om chips te verbinden, versmelt hybride bonding de koperen pads van twee wafers direct met elkaar. Dit levert een aanzienlijk hoger aantal verbindingspunten per vierkante millimeter op, waardoor het beschikbare communicatieoppervlak tussen verwerkingselementen (PE's) effectief wordt verdubbeld of verdrievoudigd, wat veel complexere netwerktopologieën mogelijk maakt in Wafer-Scale AI-systemen.

- Verhoogde interconnect-dichtheid: Hybride bonding maakt miljoenen verticale verbindingen over het waferoppervlak mogelijk.

- Verminderde parasitaire capaciteit: De directe koper-op-koper-interface verlaagt de elektrische weerstand en de energie die nodig is om bits te verzenden.

- Verbeterd thermisch beheer: Het stapelen van wafers kan de warmteafvoerpaden verbeteren in combinatie met geavanceerde vloeistofkoeling.

- Reticle-integratie: Het proces maakt naadloze communicatie mogelijk tussen de rechthoekige "reticles" (de basiseenheden van chipproductie) waaruit de wafer bestaat.

Hoe beïnvloedt fysieke reticle-plaatsing de netwerktopologie in wafer-scale chips?

De fysieke reticle-plaatsing bepaalt de haalbare netwerktopologie door de grenzen te definiëren waar snelle on-chip bedrading moet overgaan in inter-reticle of inter-wafer verbindingen. In een standaard Wafer-Scale AI-ontwerp beperkt het lithografieproces de grootte van een enkele functionele eenheid (de reticle), waardoor een stappatroon nodig is om de hele wafer te bedekken. Onderzoekers, waaronder Luca Benini, Torsten Hoefler en Maciej Besta, ontdekten dat de manier waarop deze reticles zijn uitgelijnd — of ze nu perfect gestapeld of verschoven zijn — het pad bepaalt dat gegevens moeten afleggen, wat een directe impact heeft op de latentie en doorvoer.

Geavanceerde plaatsingsstrategieën kunnen het "aantal hops" tussen ver uit elkaar gelegen verwerkingskernen aanzienlijk verminderen. Het onderzoeksteam onderzocht vier primaire configuraties: Aligned, Interleaved, Rotated en Contoured. Door de reticles tijdens het hybride bondingproces strategisch te verschuiven of te roteren, konden ze shortcut-paden creëren die in een standaard 2D-mesh onmogelijk zouden zijn. Bijvoorbeeld, een "Contoured" plaatsing stelt het netwerk in staat om de natuurlijke cirkelvorm van de wafer te volgen, waardoor het gebruik van silicium aan de randen wordt geoptimaliseerd en een efficiënter globaal communicatienetwerk voor deep learning-taken ontstaat.

Topologie optimaliseren: de vier reticle-plaatsingsstrategieën

De basis voor wafer-scale netwerken is doorgaans een 2D-mesh, die beperkt wordt door zijn rigide, rasterachtige connectiviteit. Hoewel functioneel, lijdt de 2D-mesh onder een hoge latentie wanneer gegevens van de ene kant van de wafer naar de andere moeten reizen. Om dit aan te pakken, suggereert het onderzoek van Hoefler en zijn collega's dat de fysieke opstelling van de wafers kan worden gemanipuleerd om "snelle banen" voor gegevens te creëren. De Aligned en Interleaved strategieën richten zich op het vereenvoudigen van de verticale verbindingen tussen twee gebonden wafers om te garanderen dat elke verwerkingskern een directe partner heeft op de tegenoverliggende laag.

Geavanceerde configuraties zoals de Rotated en Contoured plaatsingen betekenen een doorbraak in high-performance netwerkontwerp. De Rotated strategie houdt in dat één wafer 90 graden gedraaid wordt voor het bonden, wat de fysieke lay-out transformeert in een high-radix netwerk. Deze configuratie maakt "lange-afstands-hops" over de wafer mogelijk zonder extra fysieke bedrading toe te voegen. Deze geoptimaliseerde topologieën zorgen ervoor dat het netwerk de grillige gegevenspatronen aankan die vaak worden gezien in sparse AI-modellen, wat een flexibele infrastructuur biedt die zich kan aanpassen aan verschillende neurale netwerkarchitecturen.

De winst kwantificeren: prestaties en efficiëntie

De implementatie van geoptimaliseerde reticle-plaatsingsstrategieën resulteerde in een enorme stijging van 250% in netwerkdoorvoer vergeleken met traditionele 2D-mesh baselines. Deze prestatiesprong is voornamelijk te danken aan de vermindering van netwerkcongestie; door meer directe paden voor gegevens te bieden, kan het systeem gelijktijdig grotere volumes informatie verplaatsen. Voor Large Language Models betekent dit dat de "all-reduce" en "all-to-all" communicatiepatronen, die de training vaak vertragen, in een fractie van de tijd kunnen worden voltooid.

Naast pure snelheid benadrukt het onderzoek aanzienlijke verbeteringen in latentie en duurzaamheid op het gebied van energieverbruik.

- Latentiereductie: Communicatievertragingen werden met wel 36% verminderd, wat een snellere synchronisatie van modelgewichten mogelijk maakt.

- Energie-efficiëntie: De energie die nodig is per verzonden byte daalde met wel 38%, een cruciale maatstaf voor de milieu-impact van AI.

- Systeembetrouwbaarheid: Door het aantal hops en de elektrische afstand die gegevens moeten afleggen te verminderen, verbeterden de onderzoekers ook de algehele robuustheid van het communicatienetwerk.

Gevolgen voor de industrie: van Cerebras naar toekomstige superchips

Dit onderzoek biedt een routekaart voor de toekomst van de halfgeleiderproductie, die verder gaat dan de beperkingen van individuele GPU-chips. Hoewel bedrijven als Cerebras Systems de levensvatbaarheid van wafer-scale engines al hebben bewezen, suggereert het werk van Torsten Hoefler en zijn team aan de ETH Zurich dat we nog maar aan het begin staan van wat mogelijk is. Door gebruik te maken van wafer-on-wafer bonding en geavanceerd topologie-ontwerp, zouden toekomstige superchips biljoenen transistors in één enkele behuizing kunnen bevatten, wat de hardware biedt die nodig is om modellen te trainen die veel groter zijn dan GPT-4.

De verschuiving naar geïntegreerde Wafer-Scale AI zal waarschijnlijk de concurrentie in de markt voor AI-hardware herdefiniëren. Terwijl de vraag naar LLM's explosief blijft stijgen, zal het vermogen om het energieverbruik te minimaliseren en tegelijkertijd de doorvoer te maximaliseren het primaire concurrentievoordeel worden. De overgang van het bouwen van "clusters van chips" naar "wafer-scale systemen" vertegenwoordigt een fundamentele verandering in hoe we over computerarchitectuur denken, wat een toekomst belooft waarin de fysieke omvang van onze hardware de enige beperking is voor de intelligentie van onze modellen.

Comments

No comments yet. Be the first!