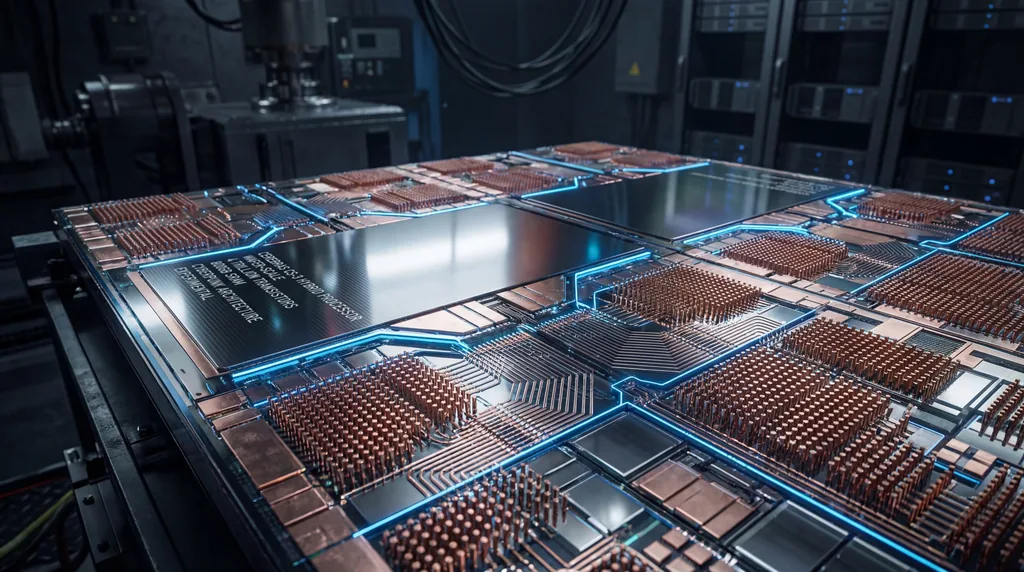

La integración de IA a escala de oblea aborda los cuellos de botella en el movimiento de datos en los LLM mediante la consolidación de cientos de miles de núcleos de procesamiento y una memoria distribuida masiva en una sola superficie de silicio continua. Este cambio arquitectónico elimina el "muro de ancho de banda" presente en los clústeres tradicionales de múltiples GPU, donde las velocidades de comunicación caen significativamente cuando los datos cruzan los límites del chip. Mediante el uso de la unión híbrida oblea sobre oblea (WoW), los investigadores han habilitado interconexiones de ancho de banda ultraalto que permiten un flujo de datos fluido en todo el sistema, facilitando el procesamiento paralelo masivo requerido para los Modelos de Lenguaje de Gran Tamaño (LLM) modernos.

El cuello de botella del movimiento de datos en la IA moderna

El principal cuello de botella para escalar los Modelos de Lenguaje de Gran Tamaño ha pasado del rendimiento computacional bruto a las limitaciones físicas del movimiento de datos entre chips individuales. En los clústeres de computación de alto rendimiento convencionales, como los que utilizan sistemas NVIDIA DGX, las GPU individuales están limitadas por los pines físicos y el cableado necesarios para comunicarse con los procesadores vecinos. Esto crea un "muro de comunicación" donde el coste energético y la latencia del movimiento de datos entre chips se convierten en los factores dominantes en el tiempo de entrenamiento y la eficiencia de la inferencia.

La latencia de interconexión crea una sobrecarga significativa durante las fases de sincronización del entrenamiento de modelos basados en Transformer. A medida que los modelos crecen hasta alcanzar billones de parámetros, la necesidad de operaciones frecuentes de "all-reduce" —donde los gradientes se comparten entre todos los nodos de procesamiento— pone a prueba el hardware de red tradicional. Esto ha dado lugar a una era de investigación "Post-GPU", en la que los informáticos buscan formas de tratar una oblea de silicio completa como un único superchip unificado para mantener el flujo de datos de alta velocidad necesario para la próxima generación de IA generativa.

¿Qué es el motor a escala de oblea de Cerebras y cómo funciona?

El motor a escala de oblea (WSE) de Cerebras es un sistema masivo en oblea que integra cientos de miles de núcleos optimizados para IA y gigabytes de SRAM en el chip en una sola pieza de silicio. Al eludir el proceso tradicional de cortar las obleas en pequeños chips individuales, el WSE mantiene el cableado de alto ancho de banda inherente al proceso de fabricación de silicio en toda la superficie de 215 mm x 215 mm. Este diseño permite una arquitectura de malla que admite comunicaciones de latencia ultrabaja, lo cual es fundamental para ejecutar operaciones limitadas por la memoria, como la inferencia de Modelos de Lenguaje de Gran Tamaño a escala.

El WSE funciona aprovechando estrategias de paralelismo especializadas, como MeshGEMM y MeshGEMV, para optimizar el acceso a la memoria distribuida. En una GPU estándar, la memoria de alto ancho de banda (HBM) se encuentra fuera del procesador, lo que crea un cuello de botella; sin embargo, el enfoque a escala de oblea sitúa la memoria directamente adyacente a los núcleos de cómputo. Esta arquitectura permite que el sistema gestione el movimiento masivo de datos requerido para el pre-llenado del modelo y la generación de tókenes sin el proceso lento y costoso en energía de recuperar datos de componentes externos, lo que resulta en un rendimiento órdenes de magnitud más rápido para las cargas de trabajo de IA.

Explicación de la integración a escala de oblea y la unión híbrida

La unión híbrida oblea sobre oblea (WoW) es una técnica de fabricación de vanguardia que apila verticalmente dos obleas de silicio para crear una interconexión 3D de alta densidad. A diferencia de los métodos de empaquetado tradicionales que utilizan micro-bumps o soldadura para conectar chips, la unión híbrida funde las almohadillas de cobre de dos obleas directamente entre sí. Esto proporciona un número significativamente mayor de puntos de conexión por milímetro cuadrado, duplicando o triplicando efectivamente el área de comunicación disponible entre los elementos de procesamiento (PE) y permitiendo topologías de red mucho más complejas en los sistemas de IA a escala de oblea.

- Mayor densidad de interconexión: La unión híbrida permite millones de conexiones verticales en toda la superficie de la oblea.

- Reducción de la capacitancia parásita: La interfaz directa cobre-cobre reduce la resistencia eléctrica y la energía necesaria para transmitir bits.

- Gestión térmica mejorada: El apilamiento de obleas puede mejorar las vías de disipación de calor cuando se combina con refrigeración líquida avanzada.

- Integración de retículas: El proceso permite una comunicación fluida entre las "retículas" rectangulares (las unidades básicas de fabricación de chips) que componen la oblea.

¿Cómo afecta la colocación física de la retícula a la topología de red en los chips a escala de oblea?

La colocación física de la retícula dicta la topología de red alcanzable al definir los límites donde el cableado de alta velocidad en el chip debe transicionar a enlaces entre retículas o entre obleas. En un diseño estándar de IA a escala de oblea, el proceso de litografía limita el tamaño de una sola unidad funcional (la retícula), lo que requiere un patrón de pasos para cubrir toda la oblea. Los investigadores, incluidos Luca Benini, Torsten Hoefler y Maciej Besta, descubrieron que la forma en que se alinean estas retículas —ya sea perfectamente apiladas o desplazadas— determina la ruta que deben seguir los datos, impactando directamente en la latencia y el rendimiento.

Las estrategias de colocación sofisticadas pueden reducir significativamente el "conteo de saltos" entre núcleos de procesamiento distantes. El equipo de investigación investigó cuatro configuraciones principales: Alineada, Intercalada, Rotada y Contorneada. Al desplazar o rotar estratégicamente las retículas durante el proceso de unión híbrida, pudieron crear rutas de acceso directo que serían imposibles en una malla 2D estándar. Por ejemplo, una colocación "Contorneada" permite que la red siga la forma circular natural de la oblea, optimizando el uso del silicio en los bordes y creando un tejido de comunicación global más eficiente para tareas de aprendizaje profundo.

Optimización de la topología: Las cuatro estrategias de colocación de retículas

La base de referencia para las redes a escala de oblea suele ser una malla 2D, que está limitada por su conectividad rígida en forma de cuadrícula. Aunque es funcional, la malla 2D sufre de una alta latencia cuando los datos deben viajar de un lado de la oblea al otro. Para abordar esto, la investigación presentada por Hoefler y sus colegas sugiere que la disposición física de las obleas se puede manipular para crear "carriles rápidos" para los datos. Las estrategias Alineada e Intercalada se centran en simplificar las conexiones verticales entre dos obleas unidas para garantizar que cada núcleo de procesamiento tenga un socio directo en la capa opuesta.

Las configuraciones avanzadas como las colocaciones Rotada y Contorneada representan un gran avance en el diseño de redes de alto rendimiento. La estrategia Rotada implica girar una oblea 90 grados antes de la unión, lo que transforma el diseño físico en una red de alto radix. Esta configuración permite saltos de "largo alcance" a través de la oblea sin añadir cableado físico adicional. Estas topologías optimizadas garantizan que la red pueda manejar los patrones de datos erráticos que se ven a menudo en los modelos de IA dispersos, proporcionando una infraestructura flexible que puede adaptarse a diferentes arquitecturas de redes neuronales.

Cuantificación de las mejoras: Rendimiento y eficiencia

La implementación de estrategias optimizadas de colocación de retículas resultó en un aumento masivo del 250% en el rendimiento de la red en comparación con las bases de referencia de malla 2D tradicionales. Este salto en el rendimiento se debe principalmente a la reducción de la congestión de la red; al proporcionar rutas más directas para los datos, el sistema puede mover mayores volúmenes de información simultáneamente. Para los Modelos de Lenguaje de Gran Tamaño, esto significa que los patrones de comunicación "all-reduce" y "all-to-all", que a menudo estancan el entrenamiento, pueden completarse en una fracción del tiempo.

Más allá de la velocidad bruta, la investigación destaca mejoras significativas en la latencia y la sostenibilidad energética.

- Reducción de la latencia: Los retrasos en la comunicación se redujeron hasta en un 36%, lo que permite una sincronización más rápida de los pesos del modelo.

- Eficiencia energética: La energía requerida por byte transmitido disminuyó hasta en un 38%, una métrica crítica para el impacto ambiental de la IA.

- Fiabilidad del sistema: Al reducir el número de saltos y la distancia eléctrica que deben recorrer los datos, los investigadores también mejoraron la robustez general del tejido de comunicación.

Implicaciones para la industria: De Cerebras a los futuros superchips

Esta investigación proporciona una hoja de ruta para el futuro de la fabricación de semiconductores, yendo más allá de los límites de los chips GPU individuales. Si bien empresas como Cerebras Systems ya han demostrado la viabilidad de los motores a escala de oblea, el trabajo de Torsten Hoefler y su equipo en la ETH Zurich sugiere que solo estamos al principio de lo que es posible. Mediante el uso de la unión oblea sobre oblea y el diseño de topología avanzada, los futuros superchips podrían albergar billones de transistores en un solo paquete, proporcionando el hardware necesario para entrenar modelos mucho más grandes que GPT-4.

El cambio hacia la IA integrada a escala de oblea probablemente redefinirá la competencia en el mercado de hardware de IA. A medida que la demanda de LLM continúa disparándose, la capacidad de minimizar el consumo de energía mientras se maximiza el rendimiento se convertirá en la principal ventaja competitiva. La transición de construir "clústeres de chips" a "sistemas a escala de oblea" representa un cambio fundamental en nuestra forma de entender la arquitectura informática, prometiendo un futuro en el que el tamaño físico de nuestro hardware sea el único límite para la inteligencia de nuestros modelos.

Comments

No comments yet. Be the first!