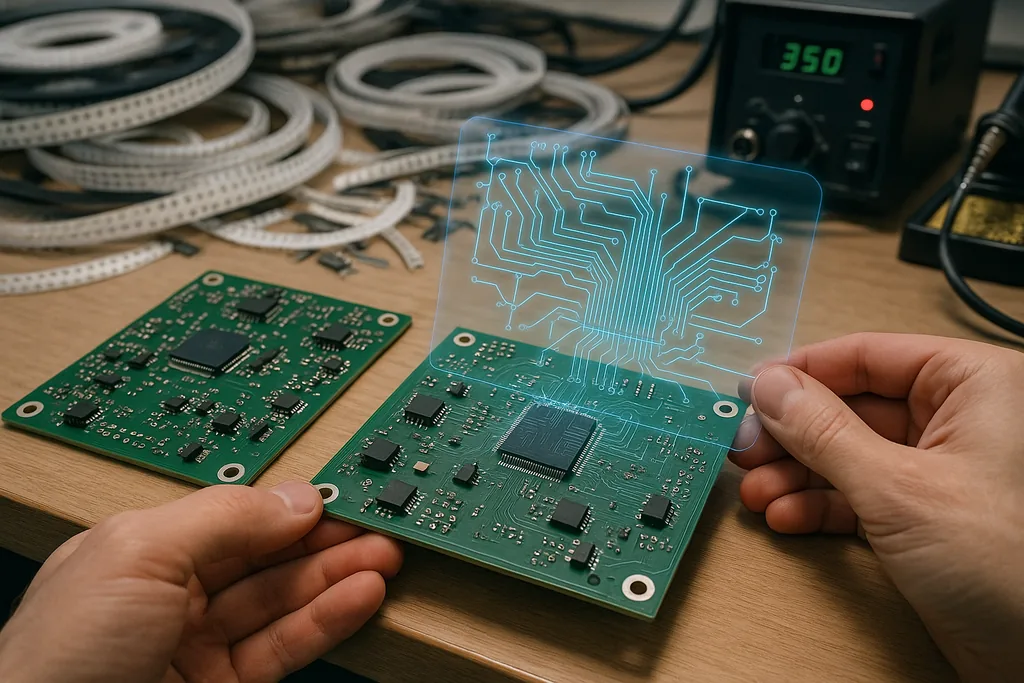

Een AI vertaalde een schema naar een werkende Linux single-board computer

Op 10 december 2025 publiceerde Quilter AI een gedetailleerd verslag van Project Speedrun: een op de NXP 8M Mini gebaseerde Linux-computer verdeeld over twee printplaten (PCB's), met 843 discrete componenten en 5.141 pinnen, waarvan het bedrijf zegt dat de door fysica aangestuurde AI de lay-out heeft bepaald en gevalideerd voordat het ontwerp werd gefabriceerd. Quilter publiceerde de ruwe AI-output, de geschoonde productiebestanden en een stap-voor-stap verslag van de validatiestappen die culmineerden in een succesvolle eerste opstart (boot) van Debian op de geassembleerde hardware. Het bedrijf stelde de ontwerpbestanden ook beschikbaar voor technici om te downloaden en te inspecteren.

Hoe het systeem van Quilter verschilt van autorouters en LLM-copiloten

Quilter positioneert zijn engine als een 'physics-first' generatief systeem: in plaats van menselijke lay-outs na te bootsen of te functioneren als een groot taalmodel dat waarschijnlijke plaatsingen voorspelt, maakt het platform gebruik van reinforcement learning en ingebouwde fysicacontroles om parallel vele kandidaat-plaatsingen en routes te verkennen. Het doel, aldus Quilter, is om signaalintegriteit, impedantiedoelen, DDR-lengteafstemming en fabricagebeperkingen in de generatie te verankeren, in plaats van ze achteraf te corrigeren in een conventionele CAD-workflow. Deze aanpak is bedoeld om teams in staat te stellen snel meerdere kandidaat-ontwerpen te produceren die klaar zijn voor fabricage, om vervolgens de beste optie te selecteren of te verfijnen in eigen CAD-tools.

Van weken handwerk naar één week en een eerste boot

Quilter rapporteert dat Project Speedrun in minder dan een week van schema naar een werkend Linux-systeem ging, waarbij mensen ongeveer 38,5 uur besteedden aan de configuratie en opschoning, terwijl de rest van de lay-out en routering door de AI werd gegenereerd. Quilter stelde dit tegenover de geraamde 428 uur voor een conventionele handmatige lay-out van vergelijkbare complexiteit. Na fabricage en assemblage startte het dual-PCB-board bij de eerste poging op en bootte Debian, waarna het tijdens de validatie gewone taken uitvoerde zoals videoweergave, een eenvoudige gamedemo en productiviteitsapplicaties. Deze beweringen zijn breed gerapporteerd in vakpublicaties en zijn gedocumenteerd in het projectmateriaal van Quilter.

Wat de geslaagde eerste boot werkelijk bewijst

Opstarten bij de eerste poging is een nuttige en tastbare mijlpaal in hardwareontwikkeling, omdat het aantoont dat de voedingsroutering, spanningsrails en basisinitialisatie van het apparaat aanwezig en correct zijn. Maar een succesvolle boot op zich is geen volledige garantie voor betrouwbaarheid op de lange termijn, thermisch gedrag onder aanhoudende belasting of signaalproblemen in randgevallen die doorgaans pas naar boven komen tijdens uitgebreide duurtesten of bij hogesnelheidsinterfaces. Vakpublicaties hebben zowel gewezen op de significantie van een eerste boot als op de beperkingen van die mijlpaal: het bewijst het concept en vermindert risico's in de vroege cyclus, maar het vervangt geen volledige validatie en kwalificatie in de praktijk. Quilters eigen documentatie toont aanvullende stresstests en vermeldt waar technici een handmatige opschoning uitvoerden voordat de bestanden naar de fabrikant werden gestuurd.

Technische keuzes en beperkingen: het 8M Mini-platform

Het Project Speedrun-systeem gebruikt een NXP 8M Mini-applicatieprocessor als computerhart — een veelgebruikte embedded ARM SoC-familie met maximaal vier Cortex-A53-cores, multimedia-acceleratie en een reeks perifere interfaces. Die keuze bepaalt de lay-outregels voor 'power islands', DDR-routering en hogesnelheidsinterfaces zoals PCIe en Gigabit Ethernet, en het geeft het validatieteam een goed gedocumenteerde set beperkingen om in de AI in te voeren. Het gebruik van een bekende, goed gekarakteriseerde SoC helpt om geautomatiseerde verificatie hanteerbaar te maken, omdat de fysicacontroles en timingbudgetten duidelijke doelen hebben om aan te voldoen.

Wat er veranderde in de workflow — en waarom dat belangrijk is

Traditionele PCB-workflows leggen een zware nadruk op menselijke expertise op het gebied van lay-out: componentclustering, ontkoppelingsgeometrie, retourpaden, differentiële paarroutering en afwegingen voor produceerbaarheid zijn allemaal vakkundige, tijdrovende handmatige taken. De visie van Quilter is dat door de repetitieve en regelgestuurde delen van dat werk te automatiseren, systeemengineers veel meer ontwerpen kunnen itereren binnen een bepaald tijdsbestek, lay-outs kunnen ontdekken die menselijke intuïtie zou missen, en menselijke tijd kunnen besteden aan systeemvraagstukken met een hogere waarde — firmware, testplannen en diagnostiek op board-niveau. Voor teams die meerdere board-varianten verzenden of evaluatieplatforms bouwen, zou die verkorting van de doorlooptijd product-roadmaps wezenlijk kunnen veranderen en de kosten van experimenteren kunnen verlagen.

Controles, vertrouwen en de noodzaak van validatie door derden

Implicaties voor toeleveringsketens, kleine teams en het halfgeleiderlandschap

Als geautomatiseerde lay-outtools de lay-outtijd betrouwbaar verkorten van maanden naar dagen, kunnen kleinere teams hardware sneller itereren en eerder beginnen met productvalidatie — een verschuiving met duidelijke gevolgen voor startups en bedrijven die afhankelijk zijn van snelle prototyping. Het zou ook kunnen veranderen waar en hoe specialistisch lay-outwerk wordt uitbesteed: routinematige lay-out zou een standaardtaak kunnen worden, terwijl deskundige lay-outengineers zich concentreren op de moeilijkste uitdagingen op het gebied van signaalintegriteit en systeemoptimalisatie. Aan de andere kant verhoogt snellere iteratie de vraag naar snelle fabricage en een betrouwbare onderdelenvoorziening, waardoor logistiek en inkoop kritieke knelpunten blijven, zelfs als lay-out dat niet meer is.

Waar verificatie, regelgeving en veiligheid een rol gaan spelen

Het automatiseren van de lay-out neemt de verantwoordelijkheden op het gebied van regelgeving niet weg. Producten in de medische, automotive- of lucht- en ruimtevaartsectoren vereisen formele ontwerpgarantie, traceerbaarheid en soms geaccrediteerde verificatieprocessen. Elke workflow die geautomatiseerde generatie introduceert, moet de herkomst waarborgen: wie heeft de beperkingen ingesteld, welke regels zijn gehandhaafd en welke controles zijn uitgevoerd voor de fabricage. De documentatie en vrijgegeven bestanden van Quilter zijn een stap in de richting van transparantie, maar gereguleerde industrieën zullen procesaudits en reproduceerbaarheid eisen voordat ze autonome lay-out-engines adopteren voor veiligheidskritische printplaten.

Wat we kunnen verwachten

Project Speedrun is eerder een vroege publieke demonstratie dan een implementatie op industriële schaal, maar het maakt duidelijk waar de innovatie naartoe gaat: fysica-bewuste generatieve systemen gekoppeld aan conventionele CAD-toolchains. De mijlpalen om de komende tijd in de gaten te houden zijn onafhankelijke verificaties door derden van door AI gegenereerde boards in diverse vormfactoren; gepubliceerde casestudy's in gereguleerde domeinen; en concurrerende reacties van gevestigde CAD-leveranciers. Hoe snel organisaties autonome lay-out zullen integreren, zal afhangen van de herhaalbaarheid van resultaten, de kosten en capaciteit van fabricagepartners en de mate waarin teams nieuwe verificatiepraktijken omarmen.

Project Speedrun herschrijft de hardware-engineering niet van de ene op de andere dag, maar het comprimeert een frictierijke fase van de workflow tot iets dat veel meer lijkt op software-iteratie: snellere kandidaten, meer tests en vroegtijdige leercycli. Dat is een betekenisvolle ontwikkeling voor iedereen die boards produceert — van hobbyisten en universitaire labs tot industriële ontwerpteams en hardware-startups. De praktische waarde zal duidelijker worden naarmate meer organisaties de bestanden van Quilter door hun eigen validatiepipelines halen en de resultaten publiceren.

Bronnen

- Quilter AI — Project Speedrun ontwerpbestanden en technische documentatie (Projectpagina en downloads)

- Quilter AI — Technische blogserie over 'physics-driven' lay-out en platformvergelijkingen

- NXP — 8M Mini productpagina en datasheet

Comments

No comments yet. Be the first!