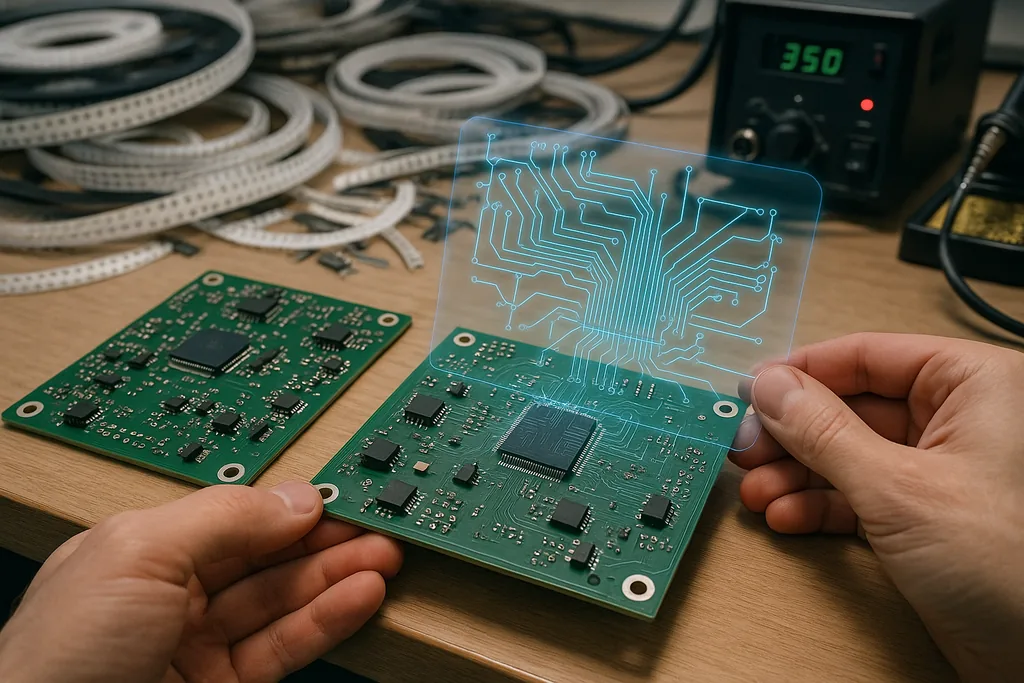

Uma IA transformou um esquema em um computador de placa única Linux funcional

Em 10 de dezembro de 2025, a Quilter AI publicou um relato detalhado do Project Speedrun: um computador Linux baseado no NXP 8M Mini dividido em duas placas de circuito impresso, contendo 843 componentes discretos e 5.141 pinos, que a empresa afirma que sua IA orientada pela física projetou o layout e validou antes do design ser fabricado. A Quilter postou a saída bruta da IA, os arquivos de produção limpos e um passo a passo das etapas de validação que culminaram em uma inicialização de primeira do Debian no hardware montado. A empresa também disponibilizou os arquivos de design para engenheiros baixarem e inspecionarem.

Como o sistema da Quilter difere de autoroteadores e copilotos de LLM

A Quilter posiciona seu motor como um sistema generativo focado primeiro na física: em vez de imitar layouts humanos ou funcionar como um modelo de linguagem de grande escala que prevê posicionamentos prováveis, a plataforma utiliza aprendizado por reforço e verificações físicas incorporadas para explorar muitos posicionamentos e rotas candidatos em paralelo. O objetivo, segundo a Quilter, é incorporar a integridade do sinal, metas de impedância, casamento de comprimento DDR e restrições de fabricação diretamente na geração, em vez de corrigi-los posteriormente em um fluxo de trabalho CAD convencional. Essa abordagem visa permitir que as equipes produzam rapidamente múltiplos candidatos prontos para fabricação e, em seguida, selecionem ou refinem a melhor opção em ferramentas CAD nativas.

De semanas de trabalho manual para uma semana e uma inicialização de primeira

A Quilter relata que o Project Speedrun passou do esquema para um sistema Linux funcional em menos de uma semana, com humanos gastando cerca de 38,5 horas em configuração e limpeza, enquanto o restante do layout e roteamento foi gerado pela IA. A Quilter contrastou isso com as 428 horas estimadas para um layout manual convencional de complexidade semelhante. Após a fabricação e montagem, a placa de PCB dupla ligou e inicializou o Debian na primeira tentativa, executando cargas de trabalho comuns, como reprodução de vídeo, uma demonstração simples de jogo e aplicativos de produtividade durante a validação. Essas afirmações foram amplamente divulgadas em coberturas especializadas e estão documentadas nos materiais do projeto da Quilter.

O que a vitória da inicialização de primeira realmente prova

Inicializar na primeira tentativa é um marco útil e tangível no desenvolvimento de hardware porque demonstra que o roteamento de alimentação, os trilhos de energia e a inicialização básica do dispositivo estão presentes e corretos. Mas o sucesso da inicialização por si só não é um endosso total da confiabilidade a longo prazo, do comportamento térmico sob carga sustentada ou de problemas de sinal em casos extremos que normalmente surgem durante testes de estresse prolongados ou em interfaces de alta velocidade. A cobertura do setor observou tanto a importância de uma inicialização de primeira quanto os limites desse marco: ele prova o conceito e reduz o risco no início do ciclo, mas não substitui a validação completa e a qualificação em campo. A própria documentação da Quilter mostra testes de estresse subsequentes e observa onde os engenheiros aplicaram uma etapa de limpeza humana antes de enviar os arquivos para o fabricante.

Escolhas técnicas e restrições: a plataforma 8M Mini

O sistema do Project Speedrun utiliza um processador de aplicação NXP 8M Mini como seu coração computacional — uma família de SoC ARM embarcada amplamente utilizada com até quatro núcleos Cortex-A53, aceleração multimídia e uma gama de interfaces periféricas. Essa escolha molda as regras de layout para ilhas de potência, roteamento DDR e interfaces de alta velocidade, como PCIe e Gigabit Ethernet, e fornece à equipe de validação um conjunto de restrições bem documentado para alimentar a IA. O uso de um SoC conhecido e bem caracterizado ajuda a tornar a verificação automatizada tratável, pois as verificações físicas e os orçamentos de tempo têm alvos claros a serem atingidos.

O que mudou no fluxo de trabalho — e por que isso importa

Os fluxos de trabalho tradicionais de PCB dão grande ênfase à experiência humana em layout: agrupamento de componentes, geometria de desacoplamento, caminhos de retorno, roteamento de pares diferenciais e compensações de fabricação são tarefas manuais que exigem habilidade e tempo. A proposta da Quilter é que, ao automatizar as partes repetitivas e orientadas por regras desse trabalho, os engenheiros de sistema podem iterar muito mais designs em uma determinada janela de tempo, descobrir layouts que a intuição humana perderia e focar o tempo humano em questões de sistema de maior valor — firmware, planos de teste e diagnósticos em nível de placa. Para equipes que enviam múltiplas variantes de placas ou constroem plataformas de avaliação, essa compressão no tempo de execução pode mudar materialmente os cronogramas de produtos e reduzir o custo de experimentação.

Verificações, confiança e a necessidade de validação de terceiros

Implicações para cadeias de suprimentos, equipes pequenas e o cenário de semicondutores

Se as ferramentas de layout automatizado comprimirem de forma confiável o tempo de layout de meses para dias, equipes menores poderão iterar o hardware mais rapidamente e iniciar a validação do produto mais cedo — uma mudança com implicações óbvias para startups e empresas que dependem de prototipagem rápida. Isso também pode mudar onde e como o trabalho especializado de layout é obtido: o layout rotineiro pode se tornar uma commodity, enquanto engenheiros de layout especialistas se concentram nos desafios mais difíceis de integridade de sinal e otimização de sistema. Por outro lado, a iteração mais rápida aumenta a demanda por fabricação de ciclo rápido e suprimento confiável de peças, de modo que a logística e a aquisição continuarão sendo gargalos críticos, mesmo que o layout deixe de ser um.

Onde a verificação, a regulamentação e a segurança entram na conversa

A automatização do layout não remove as responsabilidades regulatórias. Produtos nos domínios médico, automotivo ou aeroespacial exigem garantia de design formal, rastreabilidade e, às vezes, processos de verificação acreditados. Qualquer fluxo de trabalho que insira geração automatizada deve preservar a procedência: quem definiu as restrições, quais regras foram aplicadas e quais verificações foram realizadas antes da fabricação. A documentação e os lançamentos de arquivos da Quilter são um passo em direção à transparência, mas as indústrias regulamentadas exigirão auditorias de processo e reprodutibilidade antes de adotar motores de layout autônomos para placas críticas para a segurança.

O que observar a seguir

O Project Speedrun é uma demonstração pública inicial, em vez de uma implementação em escala industrial, mas deixa claro para onde a inovação está caminhando: sistemas generativos conscientes da física acoplados a cadeias de ferramentas CAD convencionais. Os marcos de curto prazo a serem observados são as verificações independentes de terceiros de placas geradas por IA em uma variedade de formatos; estudos de caso publicados em domínios regulamentados; e respostas competitivas de fornecedores de CAD estabelecidos. A rapidez com que as organizações incorporarão o layout autônomo dependerá da repetibilidade dos resultados, do custo e da capacidade dos parceiros de fabricação e do grau em que as equipes adotarão novas práticas de verificação.

O Project Speedrun não reescreve a engenharia de hardware da noite para o dia, mas comprime uma fase de alto atrito do fluxo de trabalho em algo que se parece muito mais com a iteração de software: candidatos mais rápidos, mais testes e ciclos de aprendizado antecipados. Esse é um desenvolvimento significativo para qualquer pessoa que projete placas — desde hobbistas e laboratórios universitários até equipes de design industrial e startups de hardware. O valor prático se tornará mais claro à medida que mais organizações passarem os arquivos da Quilter por seus próprios pipelines de validação e publicarem os resultados.

Fontes

- Quilter AI — Arquivos de design e documentação técnica do Project Speedrun (Página do projeto e downloads)

- Quilter AI — Série de blogs técnicos sobre layout orientado pela física e comparações de plataformas

- NXP — Página do produto e datasheet do 8M Mini

Comments

No comments yet. Be the first!