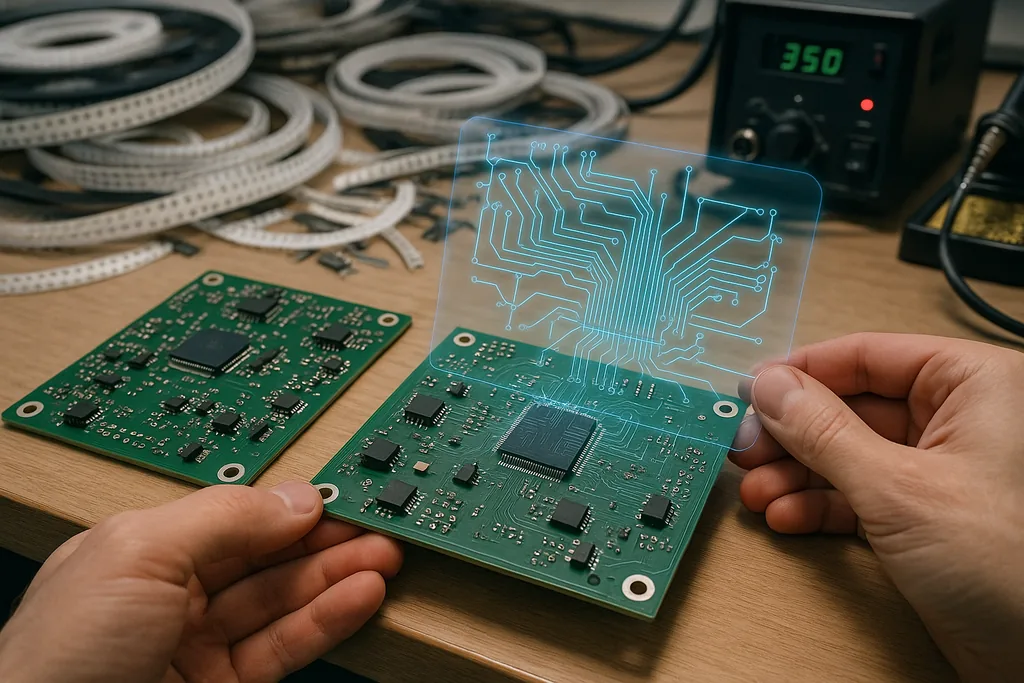

人工智能将原理图转化为可运行的 Linux 单板计算机

2025年12月10日,Quilter AI 发布了 Project Speedrun 的详细报告:这是一个基于 NXP 8M Mini 的 Linux 计算机,分布在两块印刷电路板上,包含 843 个分立元件和 5,141 个引脚。该公司表示,其物理驱动的 AI 在设计制造前完成了布局和验证。Quilter 发布了 AI 原始输出、清理后的生产文件,以及验证步骤的详细过程,最终在组装好的硬件上首次通电启动了 Debian 系统。该公司还公开了设计文件,供工程师下载和查阅。

Quilter 系统与自动布线器及大语言模型 (LLM) 助手的区别

Quilter 将其引擎定位为物理优先的生成式系统:该平台不模仿人类布局,也不像预测可能放置位置的大语言模型那样运行,而是利用强化学习和嵌入式物理检查来并行探索许多候选布局和布线方案。Quilter 表示,其目标是在生成过程中就融入信号完整性、阻抗目标、DDR 等长匹配和制造约束,而不是像传统 CAD 工作流那样在事后进行修正。这种方法旨在让团队快速生成多个可供制造的候选方案,然后在原生 CAD 工具中选择或完善最佳选项。

从数周的人工工作到一周实现首次启动

Quilter 报告称,Project Speedrun 从原理图到运行 Linux 系统耗时不到一周,其中人类花费大约 38.5 小时进行设置和清理,而其余的布局和布线均由 AI 生成。Quilter 将其与类似复杂度的传统人工布局所需的 428 小时进行了对比。经过制造和组装,这块双 PCB 板在第一次尝试时就成功通电并启动了 Debian,随后在验证期间运行了视频播放、简单的游戏演示和办公应用等普通工作负载。这些声明已在行业报道中被广泛提及,并记录在 Quilter 的项目材料中。

首次启动成功究竟证明了什么

在硬件开发中,首次尝试即成功启动是一个有用且切实的里程碑,因为它证明了电源布线、电源轨和基础设备初始化均已就绪且正确。但仅凭启动成功并不能完全代表长期可靠性、持续负载下的热行为,或是在长时间稳定性测试或高速接口中通常会出现的边缘信号问题。行业报道指出,首次启动既有重大意义也存在局限性:它验证了概念并降低了早期周期的风险,但不能取代全面的验证和实地认证。Quilter 自己的文档显示了后续的压力测试,并注明了工程师在将文件发送给制造厂之前进行了人工清理。

技术选择与约束:8M Mini 平台

Project Speedrun 系统使用 NXP 8M Mini 应用处理器作为其计算核心——这是一个广泛使用的嵌入式 ARM SoC 系列,拥有多达四个 Cortex-A53 核心、多媒体加速和一系列外设接口。这一选择决定了电源岛、DDR 布线以及 PCIe 和千兆以太网等高速接口的布局规则,并为验证团队提供了一套文档齐全的约束条件输入到 AI 中。使用已知的、特性明确的 SoC 有助于使自动化验证变得可行,因为物理检查和时序预算都有明确的目标。

工作流程发生了哪些变化——以及为什么这很重要

传统的 PCB 工作流非常强调人类的布局经验:零件聚类、去耦几何结构、回流路径、差分对布线和可制造性权衡都是极具技巧且耗时的人工任务。Quilter 的主张是,通过将这些重复性的、规则驱动的工作自动化,系统工程师可以在特定的时间窗口内进行更多次的设计迭代,发现人类直觉可能会错过的布局方案,并将精力集中在更高价值的系统问题上——如固件、测试方案和板级诊断。对于交付多种单板变体或构建评估平台的团队来说,这种开发周期的压缩可能会实质性地改变产品路线图并降低实验成本。

检查、信任与对第三方验证的需求

对供应链、小团队和半导体格局的影响

如果自动化布局工具能可靠地将布局时间从几个月压缩到几天,小团队就能更快地迭代硬件并更早开始产品验证——这一转变对初创公司和依赖快速原型的企业有着显而易见的影响。它还可能改变专业布局工作的来源:常规布局可能变成一种商品化的任务,而资深布局工程师则专注于最具挑战性的信号完整性和系统优化。另一方面,更快的迭代增加了对快速周转制造和可靠零件供应的需求,因此即使布局不再是瓶颈,物流和采购仍将是关键的制约因素。

验证、监管与安全性讨论

自动化布局并不能消除监管责任。医疗、汽车或航空航天领域的产品需要正式的设计保证、可追溯性,有时还需要经过认证的验证流程。任何引入自动化生成的流程都必须保留溯源性:谁设置了约束,执行了哪些规则,以及在制造前进行了哪些检查。Quilter 的文档和文件发布是迈向透明化的一步,但在将自主布局引擎应用于安全关键型电路板之前,受监管行业将要求进行流程审计和可重复性验证。

未来值得关注的方向

Project Speedrun 是一次早期的公开演示,而非行业规模的部署,但它明确了创新的方向:物理感知的生成式系统与传统 CAD 工具链相结合。近期值得关注的里程碑包括:第三方对各种规格 AI 生成电路板的独立验证;在受监管领域发布的案例研究;以及老牌 CAD 供应商的竞争性响应。组织采纳自主布局的速度将取决于结果的可重复性、制造伙伴的成本和产能,以及团队采用新验证实践的程度。

Project Speedrun 并没有在一夜之间改写硬件工程,但它确实将工作流中一个高摩擦的阶段压缩成了更像软件迭代的过程:更快的候选方案、更多的测试以及更早的学习循环。对于任何交付电路板的人——从爱好者、大学实验室到工业设计团队和硬件初创公司——这都是一项有意义的进展。随着更多机构通过自己的验证管线运行 Quilter 的文件并公布结果,其实际价值将变得更加清晰。

资料来源

- Quilter AI — Project Speedrun 设计文件和技术文档(项目页面及下载)

- Quilter AI — 关于物理驱动布局和平台对比的技术博客系列

- NXP — 8M Mini 产品页面和数据手册

Comments

No comments yet. Be the first!